# SMSC LAN91C100 and LAN91C110 FEAST™ Competitive Comparison in Embedded and PC Card Applications By Paul Brant

| OVERV                                                                           | /IEW                                                                 | 1           |

|---------------------------------------------------------------------------------|----------------------------------------------------------------------|-------------|

| 1.1.<br><b>1.1</b> .<br>1.2.                                                    |                                                                      | 2           |

|                                                                                 | ARISON OF 10/100 EMBEDDED ETHERNET APPLICATIONS                      |             |

| 1.3.<br>1.4.<br>1.5.<br>1.6.<br>1.7.<br>1.8.<br>1.9.<br>1.10.<br>1.11.<br>1.12. | PIN COUNT                                                            |             |

| 1.14.                                                                           | INTERRUPT LATENCY SENSITIVITYARISON RELATING TO PC CARD APPLICATIONS |             |

| 1.15.<br>1.16.<br>1.17.<br>1.18.                                                | PIN COUNT AND PACKAGE HEIGHT                                         | 7<br>7<br>7 |

| MULTI-                                                                          | -FUNCTION DESIGNS                                                    | 8           |

| 1.19.<br>1.20.<br>1.21.                                                         | FPGA DESIGN EXAMPLE                                                  | 10          |

#### **OVERVIEW**

This document will examine SMSC and competing MACs that are particularly suitable for 10/100Mbps embedded and PC Card applications. The focus will be on the differences between the available silicon and what features would be most desirable for particular applications. Specific Application examples will be offered to illustrate specific design criteria which Hardware Designers would need to consider in implementing a marketable design.

#### 1.1. 10/100 Media Access Controllers

In today's marketplace there are two basic host interfaces that all 10/100 MAC devices support. The most prevalent bus supported by MAC devices is the PCI bus. This bus is a very well understood and defined. The bus has become ubiquitous in the PC industry and has gained ground in other marketplaces as well. There are quite a number of MAC devices supporting PCI bus technology. Most, if not all Ethernet Semiconductor suppliers, including SMSC, have 10/100 Media access controllers targeted for PCI.

The other category is that of the Non-PCI Host interface 10/100 MAC Controllers. This category has fewer devices and suppliers than the PCI host interface market, and has large market demand.

#### 1.1.1. Non-PCI 10/100 Ethernet MAC Controllers

The 10/100 Ethernet MAC Non-PCI style device has a number of specific characteristics that enable solutions in the Embedded arena and Total System level market. The characteristics are:

- Processor Variance The Embedded and Total System implementation market utilize a varied set

of processor types from 8 to 16 bit low end solutions to high end 32-bit RISC, and from X86

processors to other non–X86 based systems.

- Design Complexity PCI is a cost prohibitive solution for cost sensitive embedded applications.

There are a number of processor-based solutions that do not require the bandwidth and compatibility that PCI offers. Providers of these solutions typically do not wish to worry about the critical timing, layout and other complicated hardware parameters that are required to implement a PCI system solution

- **Power Requirements** Non-PCI solutions can generally be offered to allow a more flexible power management solution than PCI for embedded designs.

- **ISA Legacy Support** The ISA bus will continue to be an active PC bus solution for the near term. There are quite a number of legacy ISA based system solutions that require networking capabilities at 10/100 Fast Ethernet data rates. PCI, obviously, would not be a viable solution.

- Other Bus Types There are quite a number of other standard busses, such as PCMCIA, CARDBUS and VME bus, which would require Fast Ethernet MAC system solutions other than PCI MAC designs.

As of the time of the printing of this application note, Non-PCI 10/100 Fast Ethernet MAC solutions are available only from SMSC and SEEQ. The next section will discuss in detail the differences between them.

#### 1.2. System Implementation

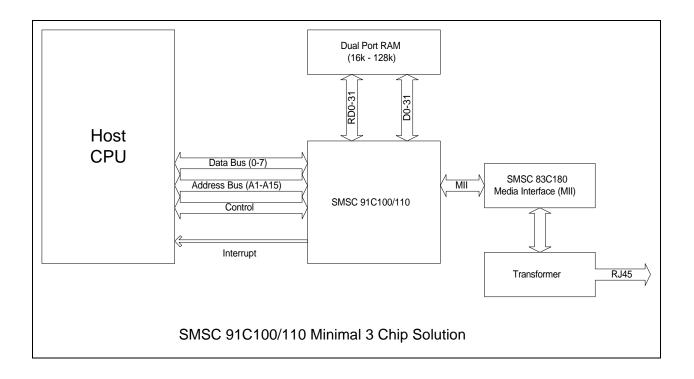

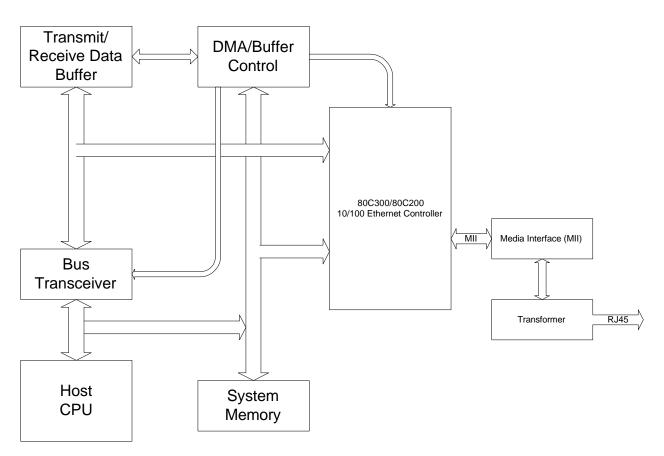

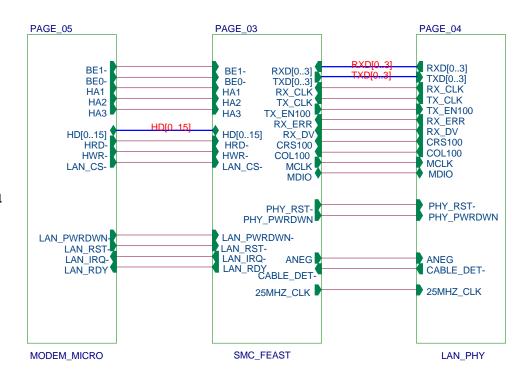

The two diagrams below show typical system implementations of Non-PCI solutions. These solutions offer different implementations of the CSMA CD MAC function. The SMSC solution implements a Dual Port Architecture with a generic "ISA-like" host interface. The data and control registers are typically implemented in I/O space, but can be mapped into memory space if necessary.

In contrast, the SEEQ device implements a FIFO based, "Cut Through" architecture relying on an external DMA controller to sink and source the TX and RX FIFO's. The following section will discuss each architecture separately.

Competitions 10/100 Ethernet Solution

#### **COMPARISON OF 10/100 EMBEDDED ETHERNET APPLICATIONS**

The table below, describes the differences between the currently available Non – PCI 10/100 Ethernet MAC Silicon in terms of features and architecture. Two offerings are from SEEQ and two are from SMSC.

| FEATURE                 | SEEQ 80C200             | SEEQ 80C300             | SMSC LAN91C100                | SMSC LAN91C110                             |

|-------------------------|-------------------------|-------------------------|-------------------------------|--------------------------------------------|

| Pin Count               | 128 Pin PQFP            | 128 Pin PQFP            | 208 Pin PQFP, VTQFP           | 144 Pin VTQFP                              |

| CPU Buss                | 8,16,32                 | 8,16                    | 8,16,32                       | 8,16                                       |

| Width Support           |                         |                         |                               |                                            |

| Memory                  | 128 byte                | 128 byte                | Dual Port RAM                 | Dual Port RAM supporting                   |

| Architecture            | Transmit /              | Transmit /              | supporting Zero Wait          | Zero Wait State Operation                  |

|                         | Receive FIFO's          | Receive FIFO's          | State Operation               | 2                                          |

| Supported               | 0.256Kbytes             | 0.256Kbytes             | 16K to 128Kbytes <sup>1</sup> | 16K to 128Kbytes <sup>2</sup>              |

| Buffer Memory           | NI.                     | NI -                    | V 0(s' 1/0                    | V = = 0(11 = 11 1/0                        |

| Built In DMA            | No                      | No                      | Yes – String I/O              | Yes – String I/O                           |

| FIFO depth              | 128bytes –<br>Static TX | 128bytes –<br>Static TX | 128Kbytes – With Dynamic MMU  | 128Kbytes – With<br>Dynamic MMU Allocation |

|                         | 128bytes –              | 128bytes –              | Allocation                    | Dynamic wivio Allocation                   |

|                         | Static RX               | Static RX               | Allocation                    |                                            |

| Early Transmit          | No                      | No                      | Yes                           | Yes                                        |

| Support                 | 110                     | 140                     | 100                           | 100                                        |

| Early Receive           | No                      | No                      | Yes                           | Yes                                        |

| Support                 |                         |                         |                               |                                            |

| Phy Layer               | MII                     | MII                     | MII, 10MB ENDEC               | MII                                        |

| support                 |                         |                         |                               |                                            |

| ISA Style Host          | No                      | No                      | Yes                           | Yes                                        |

| Interface               |                         |                         |                               |                                            |

| Multiple                | No                      | No                      | Yes – 4 Interrupt Pins        | No                                         |

| Programmable            |                         |                         |                               |                                            |

| Interrupt               |                         |                         |                               |                                            |

| Support                 | NI.                     | NI.                     | No                            | V                                          |

| Support for             | No                      | No                      | Yes                           | Yes                                        |

| Interrupt<br>Mitigation |                         |                         |                               |                                            |

| Register I/O –          | 36                      | 36                      | 16                            | 16                                         |

| Memory Foot             | 30                      | 30                      | 10                            | 10                                         |

| Print Space             |                         |                         |                               |                                            |

| required                |                         |                         |                               |                                            |

| Interrupt               | 102.4uS                 | 102.4uS                 | 102mS                         | 102mS <sup>3</sup>                         |

| Latency                 |                         |                         |                               |                                            |

| Tolerance               |                         |                         |                               |                                            |

| Solution Chip           | 6                       | 6                       | 4                             | 4                                          |

| Count                   |                         |                         |                               |                                            |

#### 1.3. **Pin Count**

All devices are in the same range in terms of pin count - the SMSC and SEEQ solutions are 208 or 144 and 128 pins respectively. Package body sizes are also similar however, note the VTQFP package height, (1.0mm), of the SMSC parts and the apparent benefits to PCMCIA applications.

<sup>&</sup>lt;sup>1</sup> Default Dual Port memory buffer size is 128k. Memory size less than 128K requires additional software

driver modification <sup>2</sup> Default Dual Port memory buffer size is 128k. Memory size less than 128K requires additional software driver modification

<sup>&</sup>lt;sup>3</sup> Interrupt Latency Tolerance is dependant on FIFO buffer depth. The 102ms value is based on 128K of Buffer RAM

## 1.4. CPU Bus Width Support

Comparing to the LAN91C110 from a standpoint of bus width, the SEEQ 80C200 device appears to have an advantage of supporting a 32-bit bus. This might seem to be a limitation of the SMSC LAN91C110 device, but in actuality, most embedded designs are limited to a 16-bit data bus. Also, some 32-bit systems will allow, and in some cases, in order to work within board space, prefer16-bit peripherals. For those designs which actually require 32-bit networking peripherals, SMSC offers the 16/32 bit bus LAN91C100FD with performance and architectural characteristics similar to that of the LAN91C110.

Embedded applications are generally designed with low cost as a primary requirement. As a result, most embedded designs employ 16 bit processors. This bus limitation is usually not a problem in terms of performance, especially at 100Mbps Ethernet data rates since the SMSC LAN91C110 has such a deep effective FIFO 128Kbyte depth. Since Ethernet is inherently "bursty", with the increased FIFO depth of the SMSC FEAST product line, performance can be maintained.

# 1.5. Memory Architecture and Supported Buffer Memory

The SMSC LAN91C110 has an overwhelming advantage over its competition in terms of memory architecture. The SMSC LAN91C110 has a patented Memory Management Architecture allowing full dynamic memory allocation for both the receive and transmit buffers. With the support for a dual port memory buffer of up to 128Kbytes, the ability for the device to buffer or queue up to 128 Kbytes of Ethernet Transmit and/or receive buffers is possible.

The performance of the SEEQ device on the other hand is very much limited by a 128byte FIFO depth and as a result, is very sensitive to FIFO over-run conditions and Interrupt Latency Tolerance.

#### 1.6. Built in DMA

The SEEQ device requires an external DMA Controller to be implemented on the board. Additional Buffer and steering logic is required as well.

The SMSC LAN91C110 device supports a Slave I/O interface that allows a simple and straightforward way to move data from and to the Host. There is a single 16/8 bit I/O port that can be mapped into I/O or memory space allowing zero wait state data accesses. With additional external DMA support, similar to the SEEQ device, DMA support can be achieved. However, this is optional and not required like it is on the SEEQ device.

## 1.7. FIFO Depth

The SEEQ Device has limited Receive and Transmit FIFO depth. The SEEQ FIFO size is 128-bytes for receive and 128-bytes for transmit. The two FIFOs are static in the sense that each FIFO is only used for either the RX or TX function. They cannot be shared.

Since the LAN91C110 and LAN91C100 devices implement a patented MMU to control allocation and deallocation of each RX and TX buffer autonomously, up to 128Kbytes of shared RX and TX buffers are available providing a much more flexible memory utilization scheme

#### 1.8. Early Transmit and Early Receive Support

Early Transmit and Receive capabilities supported by the SMSC FEAST products increase throughput by allowing the MAC device to send and receive an Ethernet packet from and to the Host or Network before the Transmit or Received packet is completely copied into the respective buffer or FIFO. As an example, if the host wants to transmit an Ethernet Packet of 1500 bytes to the LAN, without early transmit, the Ethernet MAC must copy **ALL** of the Data into a buffer. The Ethernet MAC then starts the Transmit Operation by giving a command to the Ethernet MAC to do so. In the case of an external DMA solution using the SEEQ design, the DMA controller and the appropriate data buffer needs to be setup before the transmit can continue. This is the normal non-Early Transmit situation.

For Early Transmit, the SMSC solution copies only a small portion of the Ethernet packet, approximately 64 bytes, and then immediately starts the transmit operation. This ability reduces and/or eliminates the latency for all of the host transmited Ethernet Data copied prior to Ethernet Transmit Start.

## 1.9. PHY Layer Support

Both devices support the standard IEEE Phy MII style interface.

## 1.10. Generic "ISA Style" Host interface

The SEEQ solution utilizes its own proprietary Host system interface. The SMSC solution provides a generic host interface which can be easily adapted to a wide range of system and CPU buses and conforms to the industry standard ISA interface. This interface has some distinct advantages. First, the interface is well known. There are many chip-set solutions supporting this interface. In many embedded applications such as PCMCIA and Cardbus, many multi-function interface implementations are based on a Slave I/O reference. As a result, the ISA style of interface makes a simple and cost effective solution.

## 1.11. Multiple Programmable Interrupt Support

The SEEQ device has one interrupt signal as does the LAN91C110. In comparison, the SMSC LAN91C100 supports up to 4 interrupt lines. This allows a low cost solution for ISA style designs as well as allowing embedded designs to support multiple interrupt levels. This option would be desirable in embedded "Real Time" critical applications.

## 1.12. Support for Interrupt Mitigation

The SEEQ device requires one interrupt for each Transmit and Receive event. The SMSC LAN91C110 and LAN91C100 in comparison, provides for the software driver to setup these devices to generate an interrupt on completion of multiple transmit or receive event completions allowing Interrupt optimization in time critical embedded system solutions.

# 1.13. Register I/O – Memory Foot Print Space required

SEEQ's solution requires 36 I/O or Memory locations to implement a design. SMSC's solution requires only 16 I/O locations giving the Embedded designer more latitude in the design since I/O or Memory locations can be limited.

#### 1.14. Interrupt Latency Sensitivity

The SEEQ device is very sensitive to interrupt latency in any system design due to the limited FIFO depth of the device. The Host / External DMA controller needs to be tightly coupled in order to limit FIFO overruns. Interrupt latency also adds to this tightly coupled problem. As shown in the table, the Latency numbers are derived by calculating the minimum time an interrupt must be generated to the Host and/or DMA controller in order to not overflow buffer memory.

#### Example:

SEEQ: Maximum Interrupt Latency (for 10Mb Ethernet) = 1/(10Mb/8 Bits) \* 128 Deep FIFO = 102.4uS SMSC: Maximum Interrupt Latency (for 10Mb Ethernet) = 1/(10Mb/8 Bits) \* 128K Deep FIFO = 102mS

#### Comparison relating to PC CARD Applications

The PCMCIA / Cardbus market has quite a number of solutions supporting single function devices for Ethernet and Modem ("Telco") devices. There are however, few standard device chip sets that support 16 bit CARDBUS/PCMCIA supporting Ethernet plus Modem multi-function designs.

Table 2 shown below, describes the differences between the currently available Non – PCI 10/100 Ethernet MAC Silicon in terms of implementation of Multi-function PCMCIA designs.

Table 2 - Applicability Issues to PC Card Solutions

| rubic 1 / Applicability results to 1 of each decisions |                |               |                     |                    |  |  |

|--------------------------------------------------------|----------------|---------------|---------------------|--------------------|--|--|

| DESIGN                                                 |                |               |                     |                    |  |  |

| REQUIREMENT                                            | SEEQ 80C200    | SEEQ 80C300   | SMSC LAN91C100      | SMSC LAN91C110     |  |  |

| Pin Count                                              | 128 Pin PQFP   | 128 Pin PQFP  | 208 Pin PQFP, VTQFP | 144 Pin, VTQFP     |  |  |

| CPU BusWidth                                           | 8,16,32        | 8,16          | 8,16,32             | 8,16               |  |  |

| Support (16 bit                                        |                |               |                     |                    |  |  |

| Cardbus)                                               |                |               |                     |                    |  |  |

| Total Device                                           | 7              | 7             | 5                   | 5                  |  |  |

| design Count -                                         |                |               |                     |                    |  |  |

| Single Function                                        |                |               |                     |                    |  |  |

| Total Device                                           | 8              | 8             | 6                   | 6                  |  |  |

| Count – Multi.                                         |                |               |                     |                    |  |  |

| Function <sup>4</sup>                                  |                |               |                     |                    |  |  |

| Device Package                                         | PQFP – 3.0 Mil | PQFP – 3.0Mil | PQFP – 3.0, VTQFP – | VTQFP – 1.05 (MAX) |  |  |

| Height                                                 |                |               | 1.05 (MAX)          | · ·                |  |  |

| Glue-less                                              | No             | No            | Yes                 | Yes                |  |  |

| Rockwell                                               |                |               |                     |                    |  |  |

| Modem Support                                          |                |               |                     |                    |  |  |

# 1.15. Pin Count and Package Height

The SMSC LAN91C100 and LAN91C110 are in a 208 and 144 pin package respectively. The LAN 91C110 device lends itself to space critical designs. Both of these devices have package options supporting minimal height requirements (VTQPF). SMSC's competition does not currently support minimal package heights.

## 1.16. CPU Bus Width Support

The LAN 91C100 and LAN91C110 support up to 32 and 16 bit bus widths. Even though SMSC's competition also supports similar bus widths, the dual port memory architecture of the SMSC FEAST family lends an easier design path for embedded system or Cardbus design.

## 1.17. Total Device design Count (Single and Multi-function)

As shown in the table, the SMSC solution has the obvious advantage in that fewer components are required, (ease of design and lower cost).

-

<sup>&</sup>lt;sup>4</sup>Does not include Second Function logic

# 1.18. Glue-less Rockwell Modem Support

SMSC has the advantage in the Multi-Function Cardbus and Embedded market place due to the ability to offer a solution that does not require additional glue logic. As shown in the next section, SMSC, in conjunction with technology partners such as Rockwell Semiconductor, has solutions supporting multi-function designs.

#### **Multi-Function Designs**

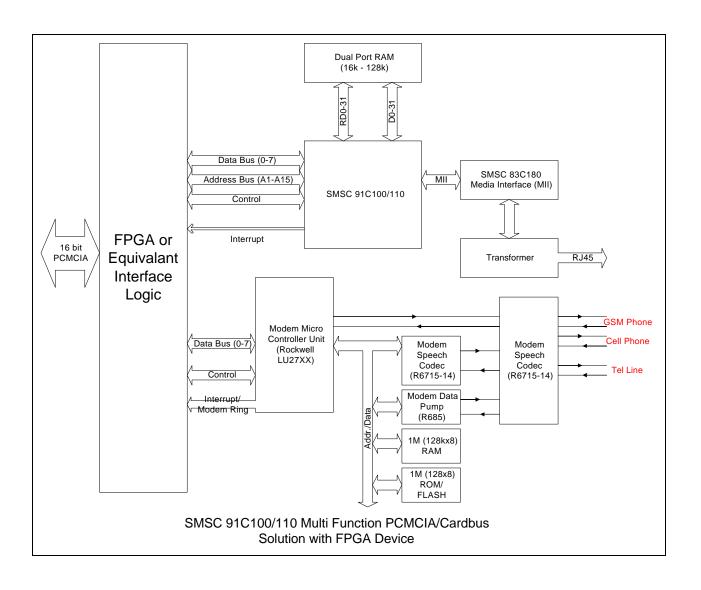

Below describes Multi-Function Cardbus design examples utilizing the SMSC LAN91C110 Ethernet Controller.

# 1.19. FPGA Design Example

The design described in the block diagram below illustrates SMSC's reference model in implementing a multi-function device. The FPGA is basically the glue logic and register set to support the additional registers required to implement PCMCIA (16 bit) multi-function designs. The Functionality in the FPGA is:

- 1. Address and decode logic for the two functions as well as the internal register set.

- 2. PCMCIA Configuration and Option register

- 3. PCMCIA Configuration and Status register

- 4. IO Base Address register

- 5. IO Ethernet Address register

- 6. PCMCIA Interrupt register

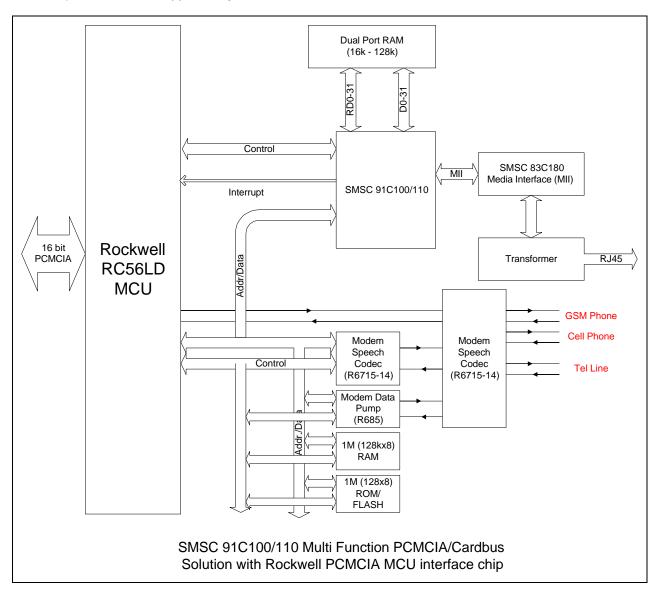

# 1.20. Rockwell / SMSC Design Example

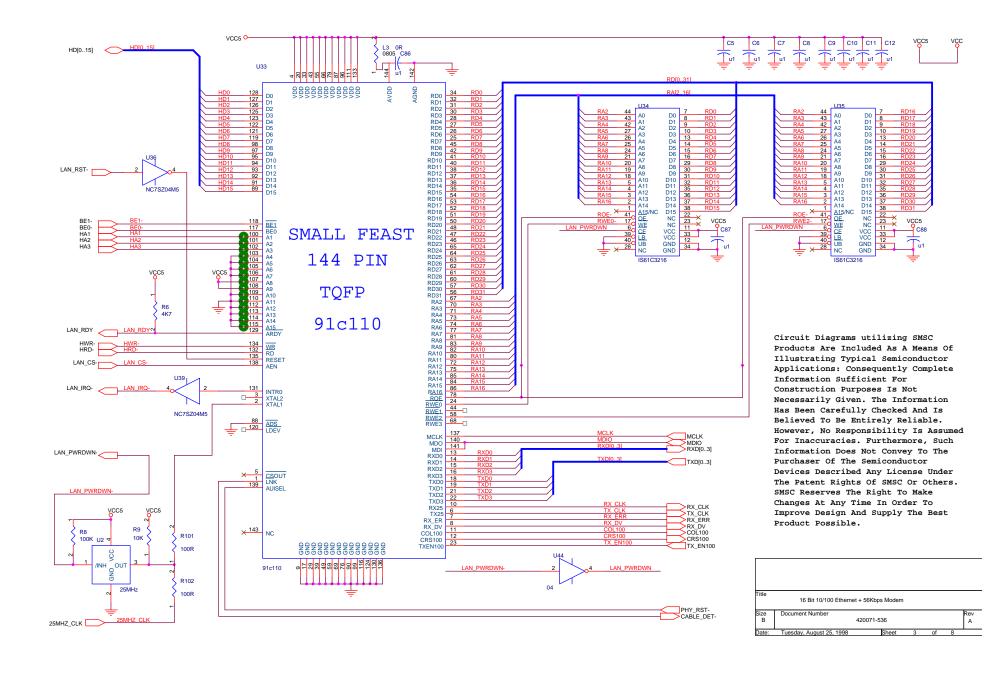

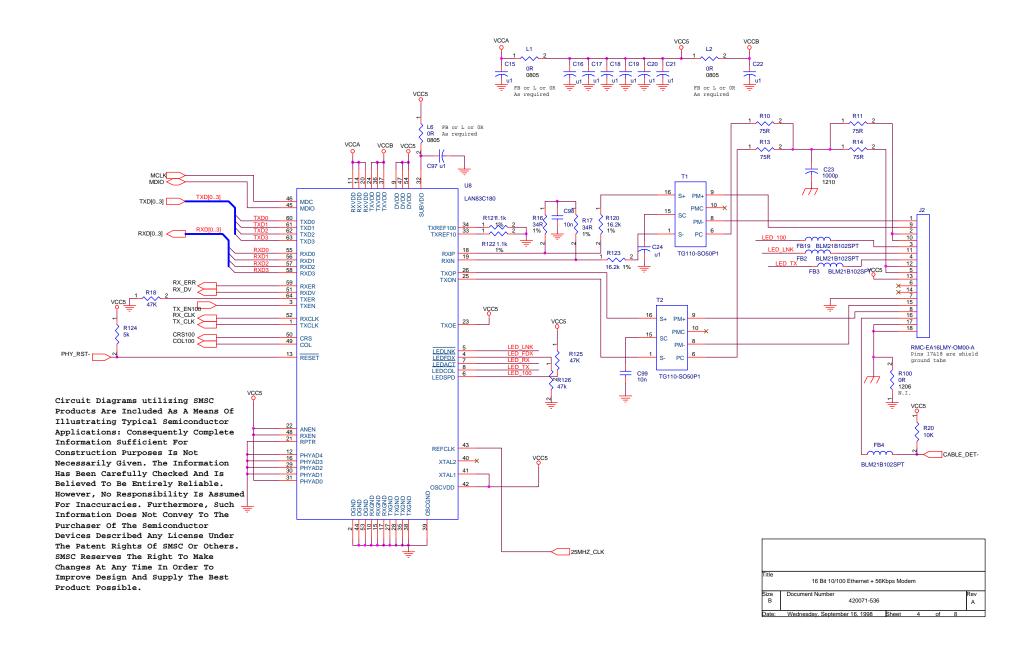

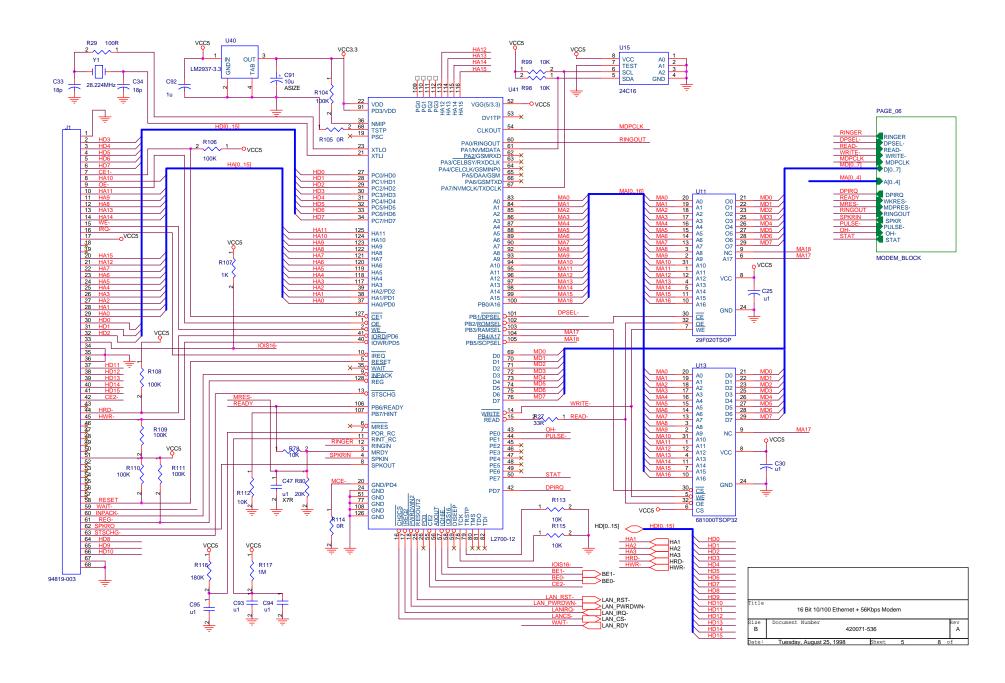

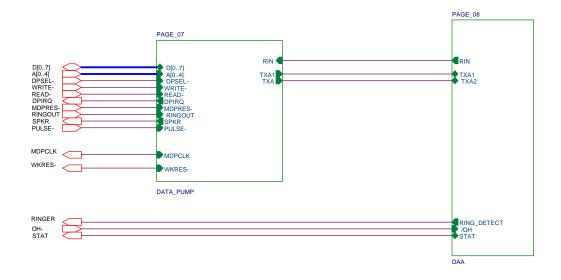

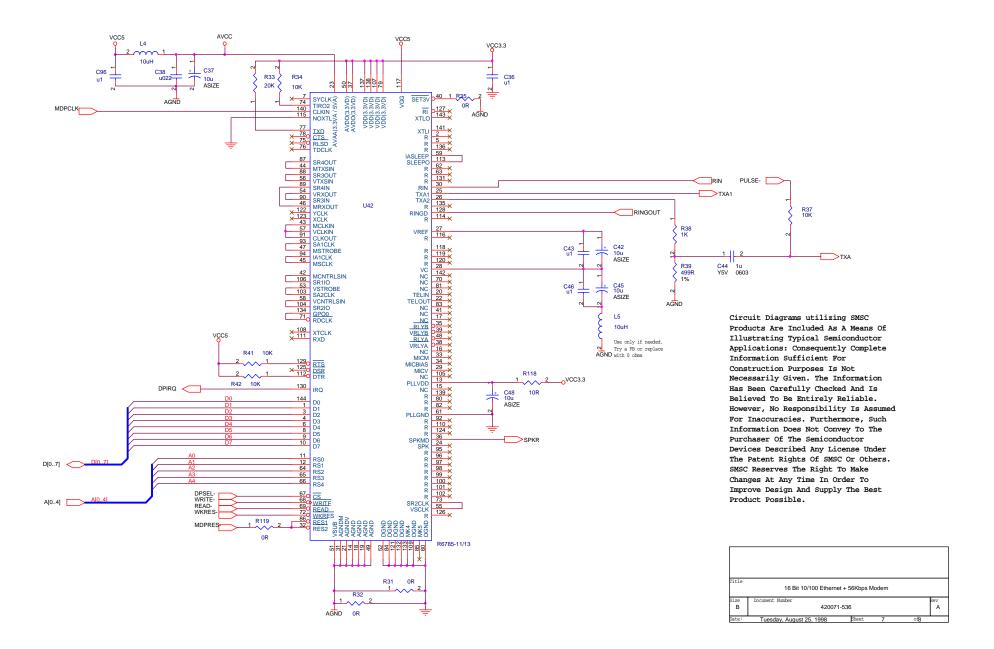

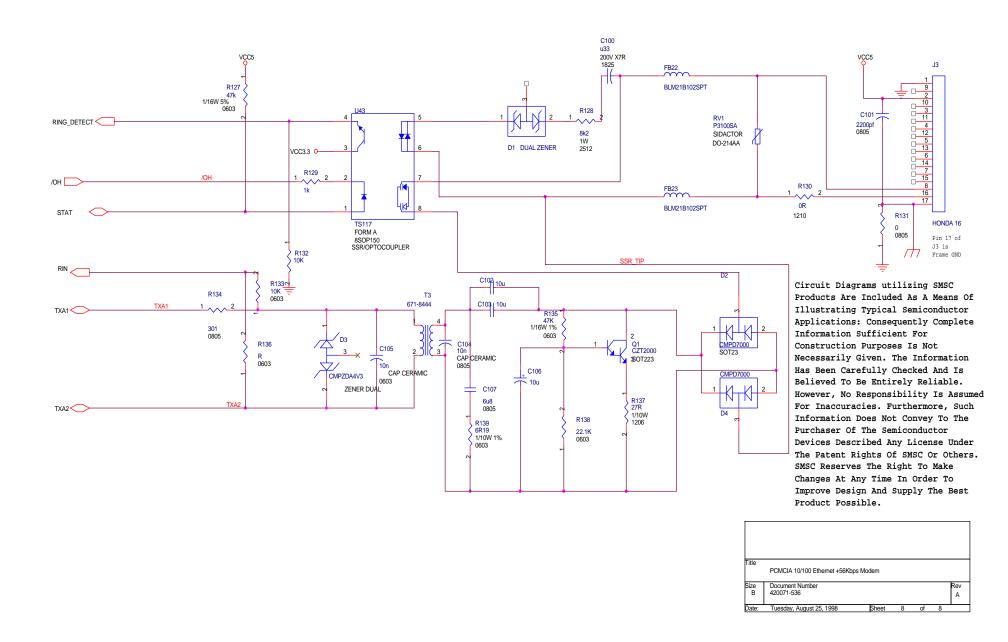

The Block Diagram described below illustrates a 16 bit PCMCIA design using the Rockwell RC56LD MCU/DSP interface device utilizing the SMSC 91C110 MAC in a PCMCIA multi-function design. The SMSC LAN 91C110 MAC interfaces to the Rockwell "Second Function" interface. There is no additional glue logic required for this interface. The RX56LD device maps the IO MAC registers into IO host space as well as routing the associated Control and Interrupt logic. The Configuration and CIS (Card Information Structure) is loaded and supported by the Rockwell device.

The Following pages are the schematics for this design. This preliminary design is included as a means of illustrating typical semiconductor applications.

Consequently, complete information sufficient for construction purposes is not necessarily given. The information has been carefully checked and is believed to be entirely reliable. However, no responsibility is assumed for inaccuracies. Furthermore, such information does not convey to the purchaser of the semiconductor devices described any license under the patent rights of SMSC or others. SMSC reserves the right to make changes at any time in order to improve design and supply the best product possible.

# 1.21. Rockwell / SMSC Design Example Schematics

Circuit Diagrams utilizing SMSC Products Are Included As A Means Of Illustrating Typical Semiconductor Applications: Consequently Complete Information Sufficient For Construction Purposes Is Not Necessarily Given. The Information Has Been Carefully Checked And Is Believed To Be Entirely Reliable. However, No Responsibility Is Assumed For Inaccuracies. Furthermore, Such Information Does Not Convey To The Purchaser Of The Semiconductor Devices Described Any License Under The Patent Rights Of SMSC Or Others. SMSC Reserves The Right To Make Changes At Any Time In Order To Improve Design And Supply The Best Product Possible.

Circuit Diagrams utilizing SMSC Products Are Included As A Means Of Illustrating Typical Semiconductor Applications: Consequently Complete Information Sufficient For Construction Purposes Is Not Necessarily Given. The Information Has Been Carefully Checked And Is Believed To Be Entirely Reliable. However, No Responsibility Is Assumed For Inaccuracies. Furthermore, Such Information Does Not Convey To The Purchaser Of The Semiconductor Devices Described Any License Under The Patent Rights Of SMSC Or Others. SMSC Reserves The Right To Make Changes At Any Time In Order To Improve Design And Supply The Best Product Possible.

80 Arkay Drive Hauppauge, NY 11788 (631) 435-6000 FAX (631) 273-3123

Copyright © SMSC 2004. All rights reserved.

Circuit diagrams and other information relating to SMSC products are included as a means of illustrating typical applications. Consequently, complete information sufficient for construction purposes is not necessarily given. Although the information has been checked and is believed to be accurate, no responsibility is assumed for inaccuracies. SMSC reserves the right to make changes to specifications and product descriptions at any time without notice. Contact your local SMSC sales office to obtain the latest specifications before placing your product order. The provision of this information does not convey to the purchaser of the described semiconductor devices any licenses under any patent rights or other intellectual property rights of SMSC or others. All sales are expressly conditional on your agreement to the terms and conditions of the most recently dated version of SMSC's standard Terms of Sale Agreement dated before the date of your order (the "Terms of Sale Agreement"). The product may contain design defects or errors known as anomalies which may cause the product's functions to deviate from published specifications. Anomaly sheets are available upon request. SMSC products are not designed, intended, authorized or warranted for use in any life support or other application where product failure could cause or contribute to personal injury or severe property damage. Any and all such uses without prior written approval of an Officer of SMSC and further testing and/or modification will be fully at the risk of the customer. Copies of this document or other SMSC literature, as well as the Terms of Sale Agreement, may be obtained by visiting SMSC's website at http://www.smsc.com. SMSC is a registered trademark of Standard Microsystems Corporation ("SMSC"). Product names and company names are the trademarks of their respective holders.

SMSC DISCLAIMS AND EXCLUDES ANY AND ALL WARRANTIES, INCLUDING WITHOUT LIMITATION ANY AND ALL IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, TITLE, AND AGAINST INFRINGEMENT AND THE LIKE, AND ANY AND ALL WARRANTIES ARISING FROM ANY COURSE OF DEALING OR USAGE OF TRADE.

IN NO EVENT SHALL SMSC BE LIABLE FOR ANY DIRECT, INCIDENTAL, INDIRECT, SPECIAL, PUNITIVE, OR CONSEQUENTIAL DAMAGES; OR FOR LOST DATA, PROFITS, SAVINGS OR REVENUES OF ANY KIND; REGARDLESS OF THE FORM OF ACTION, WHETHER BASED ON CONTRACT; TORT; NEGLIGENCE OF SMSC OR OTHERS; STRICT LIABILITY; BREACH OF WARRANTY; OR OTHERWISE; WHETHER OR NOT ANY REMEDY OF BUYER IS HELD TO HAVE FAILED OF ITS ESSENTIAL PURPOSE, AND WHETHER OR NOT SMSC HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.