# ADP2121 6 MHz Step-Down Converter Evaluation Board Documentation

**Preliminary Technical Data**

**EVAL-ADP2121**

#### **FEATURES**

600 mA synchronous step-down dc-dc converter

6 MHz operating frequency

36 µA typical no-load quiescent current in PFM mode

2.3 V to 5.5 V input voltage range\*

1.82 V fixed output voltage

Automatic power-saving mode

Tiny ceramic inductor and capacitors

### **GENERAL DESCRIPTION**

The ADP2121 evaluation module is a complete 6 MHz, low quiescent current, synchronous step down dc-to-dc converter capable of producing up to 600mA of output current at a fixed 1.82V output. The converter operates with an input voltage in

the 2.3 V to 5.5 V range. At high load currents in the device uses a voltage regulating pulse width modulation (PWM) mode that maintains a constant frequency with excellent stability and transient response. In forced PWM mode, the converter will continue operating in PWM for light loads. the At light load conditions in auto mode, the ADP2121 can automatically enter a power saving mode that utilizes pulse-frequency modulation (PFM) to reduce the effective switching frequency and ensure the longest battery life in portable applications. The evaluation module demonstrates the operation and performance of the ADP2121 as well as its compatibility with tiny ceramic components for a small-area solution.

This documentation includes I/O descriptions, setup instructions, the schematic, and the PCB Layout drawings for the ADP2121 evaluation module. See the ADP2121, 600 mA, 6 MHz Synchronous Step-Down DC-DC Converter datasheet for further operation and application information for the converter.

#### **ADP2121 EVALUATION BOARD**

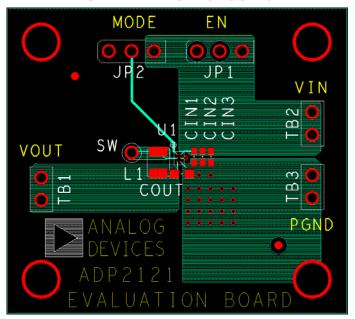

Figure 1. ADP2121 Evaluation Board

#### Rev. PrA

Evaluation boards are only intended for device evaluation and not for production purposes. Evaluation boards as supplied "as is" and without warranties of any kind, express, implied, or statutory including, but not limited to, any implied warranty of merchantability or fitness for a particular purpose. No license is granted by implication or otherwise under any patents or other intellectual property by application or use of evaluation boards. Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Analog Devices reserves the right to change devices or specifications at any time without notice. Trademarks and registered trademarks are the property of their respective owners. Evaluation boards are not authorized to be used in life support devices or systems.

<sup>\*</sup> See Application Note 2.

## **EVAL-ADP2121**

# **Preliminary Technical Data**

## **TABLE OF CONTENTS**

| Features                  | 1 |

|---------------------------|---|

| General Description       | 1 |

| ADP2121 Evaluation Board  | 1 |

| Revision History          | 2 |

| Evaluation Board Overview | 3 |

| Input/Output Connectors   | 3 |

| Evaluation Setup       | 3 |  |

|------------------------|---|--|

| Performance Evaluation | 3 |  |

| PCB Layout             | 5 |  |

| Application Notes      | 6 |  |

| FSD Caution            | 6 |  |

## **REVISION HISTORY**

3/23/08 - Rev. PrA

## **EVALUATION BOARD OVERVIEW**

The ADP2121 evaluation module is fully assembled and tested. The following section describes the various connectors on the board, the proper evaluation setup, and the testing capabilities of the evaluation module.

#### INPUT/OUTPUT CONNECTORS

#### Jumper JP1 – Enable

This connector enables or disables the converter. Connect the EN pin to GND (jumper-connect left to middle pin) to disable the converter. Connect this pin to VIN (jumper-connect right to middle pin) to enable the converter. Never leave this pin floating.

#### Jumper JP2 - Mode

This connector selects the mode of the ADP2121. Connect the MODE pin to GND (jumper-connect left to middle pin) to enable the power save mode with automatic transition from PFM mode to PWM mode. Connect the MODE pin to VIN (jumper-connect right to middle pin) to force the ADP2121 to operate in PWM mode only. Never leave this pin floating.

#### Test Bus TB1 - VOUT

This test bus is the positive connection from the output and the FB (feedback) pin of the part. Connect the positive input of the load to this bus.

#### Test Bus TB2 - VIN

This test bus provides the positive input supply voltage to the VIN pin. Connect the power supply to this bus and keep the wires as short as possible to minimize the EMI transmission.

#### Test Bus TB3 - PGND

This test bus is the ground (GND pin) connection for the part and evaluation module. Connect the return (ground) connection from the input power supply and the load to this bus.

## Test Point TP1 - SW (L1)

This test point is for measuring the switch node (SW pin) behavior. An LC filter is connected to this pin on the board. Connect a BNC cable to measure the switching frequency to this test point.

#### **EVALUATION SETUP**

Follow these setup instructions to ensure proper operation of the ADP2121 evaluation module:

- 1. Connect the positive input supply to TB2.

- 2. Connect the input supply ground to TB3.

- 3. Connect the positive load terminal to TB1 and the ground load terminal to TB3. The ADP2121 can supply up to 600 mA.

- 4. Connect JP1 to enable or disable the converter and JP2 to select between AUTO mode and PWM mode.

- 5. Apply a VIN between 2.3 V and 5.5 V (6.0 V absolute maximum.)

#### PERFORMANCE EVALUATION

The resulting oscilloscope waveforms and typical performance characteristics for the following tests are provided in the ADP2121 datasheet.

#### **Output Accuracy**

The output accuracy is verified by monitoring the output voltage (TB1) while testing both the line and load regulation.

#### **Line Regulation**

The line regulation is observed and measured by monitoring the output voltage (TB1) while varying the input voltage (TB2.)

## **Load Regulation**

The load regulation is observed and measured by monitoring the output voltage (TB1) while sweeping the applied load (between TB1 and TB3.) To minimize voltage drop, use short low resistance wires, especially for heavy loads.

## **Efficiency**

The efficiency,  $\eta$ , is measured by comparing the input power to the output power:

$$\eta = \frac{V_{out} \times I_{out}}{V_{\mathit{IN}} \times I_{\mathit{IN}}}$$

#### **PWM/PFM Transition**

To observe the PWM/PFM transition, place the converter in AUTO mode. Connect an oscilloscope to TP1 and vary load current between 70mA and 170mA. The transition point varies with input voltage and load current. Hysteresis exists in the transition point for increasing and decreasing load currents. The PWM/PFM transition will also vary depending on the VIN applied to TB2.

## **Output Ripple Voltage**

The output voltage ripple is visible by placing an oscilloscope across the output capacitor (COUT.) Set the oscilloscope to ac coupling.

#### Line transient

Generate a high speed voltage transient on the input (TB2) and observe the behavior of the evaluation module at the inductor (TP1) and the output (TB1.) Measuring with a probe directly on the output capacitor gives the most accurate measurement of the true transient.

#### Load transient

Generate a fast current transient on the output (TB1) and observe the behavior of the evaluation module at the inductor (TP1) and the output (TB1.)

## **Oscillator frequency**

The oscillator frequency can be measured by connecting an oscilloscope to TP1 with the converter in PWM mode.

## **Inductor Current**

The inductor current is made accessible by removing one side of the inductor from its pad and connecting a current loop in series. Place an oscilloscope current probe on the loop to view the current waveform.

## **PCB LAYOUT**

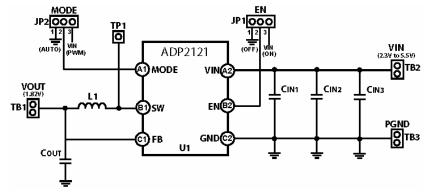

Figure 2. ADP2121 Evaluation Board Schematic

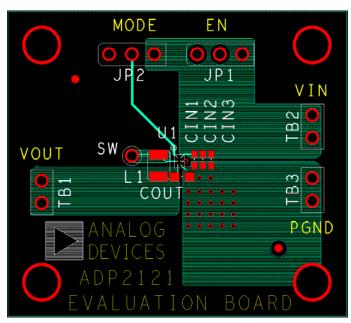

Figure 3. PCB Top Layer

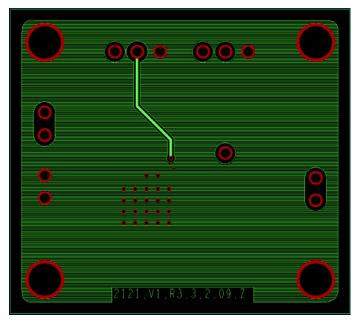

Figure 4. PCB Bottom Layer

## Table 1. Bill of Materials

| Description                                              | Reference Designator            | Qty | Manufacturer         | Part Number        |

|----------------------------------------------------------|---------------------------------|-----|----------------------|--------------------|

| ADP2121 Step-down Converter                              | U1                              | 1   | Analog Devices, Inc. | ADP2121            |

| Capacitor, MLCC, 2.2 μF, 4 V, 0402, X5R                  | CIN1                            | 1   | Murata               | GRM155R60J225ME15D |

| Capacitor, MLCC, 4.7 μF, 6.3V, 0402, X5R                 | CIN2, CIN3, COUT                | 3   | Murata               | GRM155R60J475ME87D |

| Inductor, 0.47μH, 0805                                   | L1                              | 1   | Murata               | LQM21PNR47MC0D     |

| Headers, 0.10 in, single/double row/triple row, Straight | JP1, JP2, TP1, TB1, TB2,<br>TB3 | 13  | Sullins Electronics  | PBC36SAAN          |

## **APPLICATION NOTES**

- 1. It is recommended that the VIN pin be bypassed with a  $2.2~\mu F$  or larger ceramic input capacitor if your supply line has a distributed capacitance of at least  $10~\mu F$ . If not, at least a  $10~\mu F$  capacitor is recommended on the input supply pin. The input capacitor can be increased without any limit for better input voltage filtering.

- 2. Maximum output current capability at minimum VIN of 2.3 V is 300mA. The maximum output current guarantee for 2.3 V to 2.5 V increases linearly from 300 mA to 500 mA. The maximum output current guarantee for 2.5 V to 2.7 V increases linearly from 500 mA to 600 mA. Above 2.7 V, the maximum output current guarantee is 600 mA.

## **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.