# 3.3V, 1.25Gbps PECL High-Sensitivity Limiting Post Amplifier with TTL Signal Detect

### SY88933AL Evaluation Board

### **General Description**

The SY88933AL high-sensitivity, limiting post amplifier is designed for use in fiber-optic receivers. The device connects to typical transimpedance amplifiers (TIAs). The linear signal output from TIAs can contain significant amounts of noise and may vary in amplitude over time. The SY88933AL quantizes these signals and outputs PECL-level waveforms.

The SY88933AL operates from a single +3.3V power supply, over an industrial temperature range of  $-40^{\circ}$ C to +85°C. With its wide bandwidth and high gain signals with data rates up to 1.25Gbps and as small as  $5\text{mV}_{pp}$  can be amplified to drive devices with PECL inputs.

The SY88933AL generates a high-gain, signal-detect (SD), open-collector, TTL output. The SD function has a high gain input stage for increased sensitivity. A programmable signal-detect level set pin (SD<sub>LVL</sub>) sets the sensitivity of the input amplitude detection. SD asserts high if the input amplitude rises above the threshold set by SD<sub>LVL</sub> and de-asserts low otherwise. The enable input (EN) de-asserts the true output signal without removing the input signal. The SD output can be fed back to the enable (EN) input to maintain output stability under a loss-of-signal condition. Typically, 3.4dB SD hysteresis is provided to prevent chattering.

This manual provides information on the SY88933AL evaluation board. It should be used in conjunction with the SY88933AL data sheet, which contains full specifications of the SY88933AL.

The SY88933AL evaluation board enables fast and thorough evaluation of the SY88933AL. The board is an easy-to-use, single supply design. It's designed to be driven by a high-speed, pattern generator and provides onboard  $50\Omega$  terminations for the generator's outputs. The input termination network also provides the required input bias of  $V_{CC}$ -1.3V for the SY88933AL.

The SY88933AL evaluation board is intended to terminate to a  $50\Omega$  scope and provides for simple user adjustability of the SD threshold through the adjustment of an on-board potentiometer.

All data sheets and support documentation can be on Micrel's web site at: www.micrel.com.

### **Features**

- Single 3.3V supply

- DC-to-1.25Gbps operation

- · Low-noise PECL data outputs

- High-gain SD

Chatter-free open-collector TTL signal detect (SD) output with internal 4.75kΩ pull-up resistor

- TTL EN input

- Programmable SD level set (SD<sub>LVL</sub>)

- Available in a tiny 10-pin MSOP

- AC-coupled I/O with SMA connectors

- 50Ω input network termination

#### Related Documentation

SY88933AL, 3.3V, 1.25Gbps PECL High-Sensitivity Limiting Post Amplifier w/ TTL SD Data Sheet

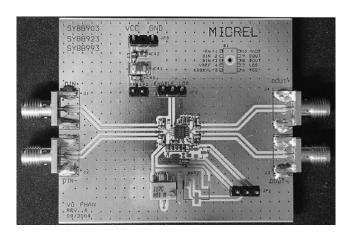

### **Evaluation Board**

Micrel Inc. • 2180 Fortune Drive • San Jose, CA 95131 • USA • tel +1 (408) 944-0800 • fax + 1 (408) 474-1000 • http://www.micrel.com

# **Measurement Setup**

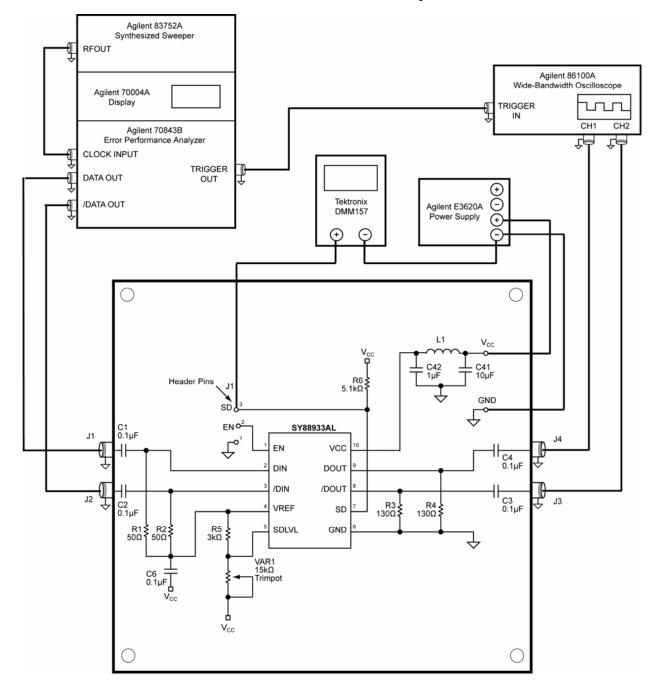

Equipment used for measurements:

- 1. Agilent 83752A Synthesized Sweeper

- 2. Agilent 70004A Display

- 3. Agilent 70843B Error Performance Analyzer

- 4. Agilent 86100A Wide-Bandwidth Oscilloscope

- 5. Two (2) MCL BW S15W2 40dB Attenuators

- 6. Agilent E3620A DC Power Supply

- 7. Tektronix DMM157 Multimeter

- 8. Matched High-Speed Cables w/SMA Connectors

Note:

Items 1 through 3 constitute the BERT stack

Figure 1. Setup for Measurement

### **Setup for Measurements**

This section explains how to connect and setup the SY88933AL evaluation board per Figure 1. Ensure proper ESD precautionary measures are taken before handling sensitive electronic equipment, including the SY88933AL evaluation board.

- 1. Set E3620A output to 3.3V and then turn off E3620A. Connect E3620A's positive lead to V<sub>CC</sub> post, negative lead to GND post.

- 2. Configure Agilent BERT stack:

- a. Set the 83752A Synthesized Sweeper to 1.25GHz.

- b. From the 70004A's Pattern menu, choose the PRBS 2<sup>23</sup>–1 pattern.

- c. From the 70004A's Trigger menu:

- i. Choose clock as trigger output

- ii. Choose CLK/8 for divider

- d. From the 70004A's Data menu:

- i. External Termination = DC termination ٥v

- ii. Attenuation = 40dB

- iii. Amplitude =  $5mV (10mV_{pp})$

- iv. Hi-Level = 0V

- v. Tracking = ON

- vi. Polarity = NORMAL

- vii. Data Output = ON

- viii. Crossing = 0

- Connect 70843V's trigger output 86100A's trigger input.

- 4. Use J1 to short /EN to GND on SY88933AL evaluation board.

- 5. Connect DIN and /DIN on SY88933AL evaluation board to 70843V's data outputs through 40dB attenuators

- a. Connect 40dB attenuators directly to the board rater than the 70843V's data outputs to allow a larger and cleaner signal to pass through the connecting SMA cables.

- 6. Connect DOUT and /DOUT on SY88933AL evaluation board to 86100A's inputs.

- 7. Set DMM157 to display voltage. Connect positive lead to LOS header on J1 and connect negative lead to GND.

- Turn on E3620A. Typical power supply be ~45mA, including the current should SY88933AL's current and current through the on-board 200 $\Omega$  output pull-down resistors at 3.3V supply voltage. Excessive current usually means the power supply leads have been connected backwards. Be careful of this!

- 9. To configure 86100A oscilloscope:

- a. Verify a trigger signal is present by checking that the Trigger Source button is lit.

- i. Depress this button to choose external source if necessary.

- ii. Adjust trigger level if necessary.

- b. Press Eye/Mask Mode on front panel.

- c. Choose NRZ Eye Measurements from on-screen display.

- d. Choose RMS Jitter, Rise Time, Fall Time and Eye Amplitude measurements from on-screen selection list.

#### Measurements

The SY88933AL evaluation board assumes the use of a  $50\Omega$  scope to terminate the SY88933AL. The following sections detail various metrics that the SY88933AL evaluation board can measure:

- 1. Eye pattern generation including jitter and rise/fall times:

- a. Set 70004's Data amplitude to 5mV  $(10mV_{pp}).$

- b. Press Autoscale on oscilloscope. The eve pattern should automatically display on the scope. If not, verify the steps listed in the "Setup for Measurements" section are completed. Sometimes the waveform needs to be manually adjusted to fit the display. Use the Time Scale and Voltage Scale knobs on the front panel of the scope to adjust this.

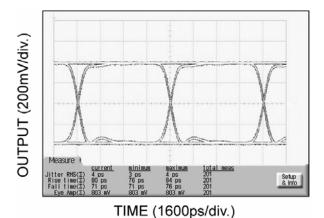

- c. Observe measurements on scope's display. The rise and fall times should be less than 120ps, amplitude around 400mV (800mV<sub>pp</sub>) and jitter around 10ps<sub>rms</sub>.

- Note that the output amplitude varies with the input amplitude until the SY88933AL enters limiting mode at around 20mV<sub>pp</sub> input. The SY88933AL has a typical gain of 38dB. Hence, 10mVpp input will give only 800mV<sub>pp</sub> output, whereas 40mVpp input will give 1600mVpp output.

Figure 2. Typical SY88933AL Eye Pattern

#### 2. Mask testing:

- a. Press Eye/Mask Mode on front panel of scope.

- b. Choose Mask Testing from on-screen display.

- c. Choose Open Mask from on-screen selection list.

- i. Select and open the appropriate Mask

- d. Choose Start Mask Testing from onscreen selection list. Waveform should automatically display with appropriate mask regions and testing will start. If not, verify the steps listed in the "Setup for Measurements" section are completed.

### 3. BER testing:

- a. Feedback the SY88933AL evaluation board's DOUT output to the 70843V's BERT Data input.

- b. Feedback the 70843V's Clock output to the 70843V's BERT Clock input.

- c. Set 70004's Data amplitude to 5mV  $(10mV_{pp}).$

- d. From the 70004A's Gating menu:

- Choose a gate condition. The options are: gate by time, errors or bits. Choose bits, but this is of no relevance because there should be no errors, and the test will run forever until manually interrupted if gate by errors is chosen.

- ii. Choose single gating period

- iii. Choose run gating

- iv. 70004A will reset error count and synchronize SY88933AL's transmitted bit stream to 70843V's generated bit stream. If synchronization does not occur, it is sometimes due to cable length. Try using different length cables to achieve synchronization. If this is unavailable, another trick is to adjust the 83752A's frequency to a slightly higher or lower value.

- At end of gating period, there should be no errors.

#### 4. SD hysteresis:

a. The SY88933AL evaluation board provides a potentiometer to allow for easy adjustment of SD<sub>LVL</sub> without the need for an extra power supply. SD<sub>LVL</sub> taps off the potentiometer whose ends are connected from V<sub>CC</sub> to V<sub>REF</sub>. V<sub>REF</sub> is a reference voltage of approximately V<sub>CC</sub>-1.3V. Hence, SD<sub>LVL</sub> can be set to any voltage from  $V_{CC}$  to  $V_{CC}$ –1.2V, as specified in the SY88933AL data sheet. The potentiometer creates a voltage divider. Thus,

$$SD_{LVL} = V_{CC}(V) - 1.3V \times R(k\Omega)/15k\Omega$$

Where R is the resistance of the potentiometer from V<sub>CC</sub> to the tap at SDLVL, the proceeding steps show how to find the SD hysteresis for a 10mVpp SD assert voltage without measuring R

- b. Set 70004's Data amplitude to 5mV  $(10 \text{mV}_{pp}).$

- c. Verify DMM157 displays that SD is LOW.

- d. If not, turn R3 until SD is LOW.

- e. Slowly increase 70004A's Data amplitude until SD becomes HIGH. Note the voltage at which SD becomes HIGH. This is the SD de-assert voltage.

- f. Now slowly lower the 70004A's Data amplitude until SD becomes LOW again. This should be the starting voltage of 5mV (10mV<sub>pp</sub>). This is the SD de-assert voltage.

- g. Hysteresis(dB) = 20log(SD de-assert voltage/SD assert voltage). This should be > 2dB.

### **Evaluation Board Layout**

The SY88933AL evaluation board enables fast and thorough evaluation of the SY88933AL 1.25Gbps PECL High-Sensitivity Limiting Post Amplifier with TTL Signal Detect. The board is an easy-to-use, 4-layer high-speed coplanar design that uses Rogers 4003 dielectric material to achieve high bandwidth. The layer stack is shown in Table 1.

| Layer | Definition |  |  |

|-------|------------|--|--|

| L1    | Signal/GND |  |  |

| L2    | GND        |  |  |

| L3    | VCC        |  |  |

| L4    | GND        |  |  |

Table 1. Layer Stack

### **Frequently Asked Questions**

### I just got my SY88933AL evaluation board and I cannot get anything to work. What should I check first?

First, check the power supplies. Typical power supply current should be ~45mA including the SY88933AL current and current through the on-board 130Ω output pull-down resistors at 3.3V supply voltage. Excessive current usually means the power supply leads have been connected backwards. Be careful of this!

If the power supplies are fine, the SY88933AL is enabled and has sufficient amplitude to drive the evaluation board, and there is still nothing displaying on the scope, then there's most likely a trigger setup issue with the scope. Look on the scope's front panel and verify that the instrument is triggered. The Trigger Source button should be lit if a trigger signal is present. If not, press the button until the external trigger is selected. Also, try adjusting the level until a signal is found. If this does not work, verify that the 70004A is set to output a CLK/8 trigger signal as described in the "Setup for Measurements" section of this document.

### Can you suggest a bypass/decoupling scheme?

Figure 2 shows the power supply decoupling scheme used for the SY88933AL evaluation board. The "Bill of Materials" at the end of this document lists the supplier and component values. We have found this arrangement to be an excellent starting point.

### What layout tips do you have?

- 1. Establish controlled impedance stripline. microstrip, or coplanar construction techniques for high-speed signal paths.

- 2. All differential paths are critical timing paths and skew should be matched to within ±10ps.

- 3. Signal trace impedance should not vary more than ±5%. If in doubt, perform Time Domain Reflectometry (TDR) analysis of signal traces.

- 4. Place power supply decoupling capacitors as close as possible to the device's power pins.

#### What is Time Domain Reflectometry (TDR)?

TDR is used to verify impedance continuity along a signal path. Many interconnects, such as SMA, if not launched correctly onto the PCB, will exhibit inductivelike resonance with an abrupt capacitive discontinuity. This discontinuity will subtract signal from the inputs and outputs, effectively closing the resulting data eye. The 86100A allows TDR testing and is a useful tool to help evaluate your PCB.

### I still have questions. Who should I contact?

Micrel's HBW Applications hotline is available to assist you. Please call (408) 955-1690 or e-mail hbwhelp@micrel.com for assistance.

6 June 2005 M9999-062705

# **Bill of Materials**

| Item                            | Part Number     | Manufacturer                      | Description                                                   | Qty. |

|---------------------------------|-----------------|-----------------------------------|---------------------------------------------------------------|------|

| C1, C2, C3,C4,<br>C21, C23, C25 | VJ0402Y104KXXAT | Vishay <sup>(1)</sup>             | 0.1µF Surface Mount Capacitor, Size 0402                      | 7    |

| C20, C22, C24                   | VJ0402Y222KXXAT | Vishay <sup>(1)</sup>             | 220pF Surface Mount Capacitor, Size 0402                      | 3    |

| C41                             | 293D106X0025CT  | Vishay <sup>(1)</sup>             | 10μF Surface Mount Capacitor, Size C                          | 1    |

| C42                             | 293D105X0025CT  | Vishay <sup>(1)</sup>             | 1μF Surface Mount Capacitor, Size C                           | 1    |

| L1                              | BLM21A102F      | Murata <sup>(2)</sup>             | Ferrite Bead, Size 0603                                       | 1    |

| J1, VCC                         | TSW-103-07-S-S  | Samtec <sup>(3)</sup>             | 0.1mil Center through hole terminal strip                     |      |

| R1, R2                          | CRCW040249R9F   | Vishay <sup>(1)</sup>             | 49.9Ω Surface Mount Resistor, Size 0402                       | 2    |

| VAR1                            | 3269W-1-153G    | Bourns <sup>(4)</sup>             | 15kΩ Trimmer                                                  | 1    |

| R3, R4                          | CRCW04021300F   | Vishay <sup>(1)</sup>             | 130Ω Surface Mount Resistor, Size 0402                        | 2    |

| R5                              | CRCW04023001F   | Vishay <sup>(1)</sup>             | 3kΩ Surface Mount Resistor, Size 0402                         | 1    |

| R7                              | CRCW04025001F   | Vishay <sup>(1)</sup>             | 5kΩ Surface Mount Resistor, Size 0402                         | 1    |

| J1-J4                           | 142-0701-851    | Johnson Components <sup>(1)</sup> | End Launch SMA                                                | 4    |

| U1                              | SY88933AL       | Micrel <sup>(5)</sup>             | 3.3V 1.25Gbps CML Low-Power Limiting Post Amplifier w/ TTL SD | 1    |

#### Notes:

1. Vishay: www.vishay.com. 2. Murata: www.murata.com. 3. Samtec: www.samtec.com. 4. Bourns: www.bourns.com.

5. Johnson Components: www.johnsoncomponents.com.

6. Micrel, Inc.: www.micrel.com.

### **HBW Support**

Hotline: 408-955-1690

Email Support: <a href="mailto:HBWHelp@micrel.com">HBWHelp@micrel.com</a>

## **Application Hints and Notes**

For application notes on high speed termination on PECL and LVPECL products, clock synthesizer products, SONET jitter measurement, and other High Bandwidth product go to Micrel's website at <a href="http://www.micrel.com/">http://www.micrel.com/</a>. Once in Micrel's website, follow the steps below:

- 1. Click on "Product Info".

- In the Applications Information Box, choose "Application Hints and Application Notes."

### MICREL, INC. 2180 FORTUNE DRIVE SAN JOSE, CA 95131 USA

TEL +1 (408) 944-0800 FAX +1 (408) 474-1000 WEB http://www.micrel.com

The information furnished by Micrel in this data sheet is believed to be accurate and reliable. However, no responsibility is assumed by Micrel for its use. Micrel reserves the right to change circuitry and specifications at any time without notification to the customer.

Micrel Products are not designed or authorized for use as components in life support appliances, devices or systems where malfunction of a product can reasonably be expected to result in personal injury. Life support devices or systems are devices or systems that (a) are intended for surgical implant into the body or (b) support or sustain life, and whose failure to perform can be reasonably expected to result in a significant injury to the user. A Purchaser's use or sale of Micrel Products for use in life support appliances, devices or systems is a Purchaser's own risk and Purchaser agrees to fully indemnify Micrel for any damages resulting from such use or sale.

© 2005 Micrel, Incorporated.