# TI Precision Designs: Reference Design AC Coupled Single Supply Comparator

#### **TI Precision Designs**

TI Precision Designs are analog solutions created by TI's analog experts. Reference Designs offer the theory, component selection, and simulation of useful circuits. Circuit modifications that help to meet alternate design goals are also discussed.

#### **Design Resources**

Design Archive TINA-TI™ TLV3501 All Design files SPICE Simulator Product Folder

## **Circuit Description**

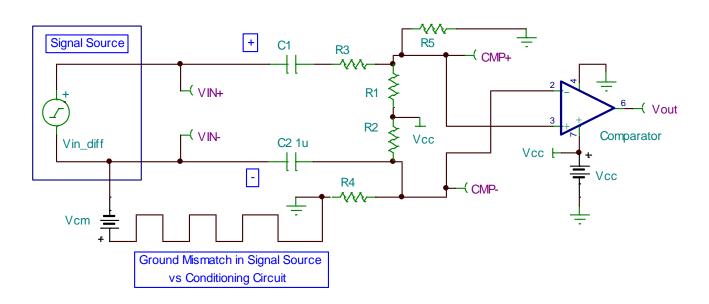

Sometimes a single supply comparator is required to use ac coupling to detect sine waves or square waves. Often this is needed due to differences in ground potential between two different modules. Whenever ac coupling is involved in single supply circuitry, negative voltages become a concern. Excessive negative voltages on comparators can cause the comparator to trip erroneously or to become stuck at unpredictable levels. Proper high pass filtering and dc offsetting are required for reliable operation. This design will show how to ac couple a wide range of input signal levels and frequencies into a high speed comparator to generate a robust and accurate clock signal.

Ask The Analog Experts

WEBENCH® Design Center

TI Precision Designs Library

A

An IMPORTANT NOTICE at the end of this TI reference design addresses authorized use, intellectual property matters and other important disclaimers and information.

TINA-TI is a trademark of Texas Instruments WEBENCH is a registered trademark of Texas Instruments

# 1 Design Summary

The design requirements are as follows:

- No Input Signal → Comparator Output = 0V

- Start-up Time < 1ms

- Supply Voltage: 3.3V, <u>+</u>5% (3.135V to 3.465V)

- Input Signal Source Supplies:

- Vcc = 3.3V,  $\pm 5\%$  (3.135V to 3.465V)

- $Vcc = 5V, \pm 5\%, (4.75V \text{ to } 5.25V)$

- Input Signal Levels:

- VIL = GND+400mV @ Isink = 2mA

- VIH = Vcc-400mV @ Isource = 2mA

- Common Mode Range: <u>+</u>100mV

- Propagation Delay: <5ns

- Duty Cycle Change from Input to Output: <10%</li>

- Frequency Requirements See Table 1

**Table 1. Input Signal Frequency Requirements**

| Frequency | Min VIL | Max VIL | Min VIH        | Max VIH        | Vcm      | Duty Cycle |

|-----------|---------|---------|----------------|----------------|----------|------------|

| 2kHz      | 0V      | 400mV   | +2.7V / +4.35V | +3.5V / +5.25V | +/-100mV | 40% to 60% |

| 32MHz     | 0V      | 400mV   | +2.7V / +4.35V | +3.5V / +5.25V | +/-100mV | 40% to 60% |

| Frequency | Period  | Duty Cycle | t <sub>on</sub> |

|-----------|---------|------------|-----------------|

| 2kHz      | 500us   | 40%        | 200us           |

| 2kHz      | 500us   | 60%        | 300us           |

| 32MHz     | 31.25ns | 40%        | 12.5ns          |

| 32MHz     | 31.25ns | 60%        | 18.75ns         |

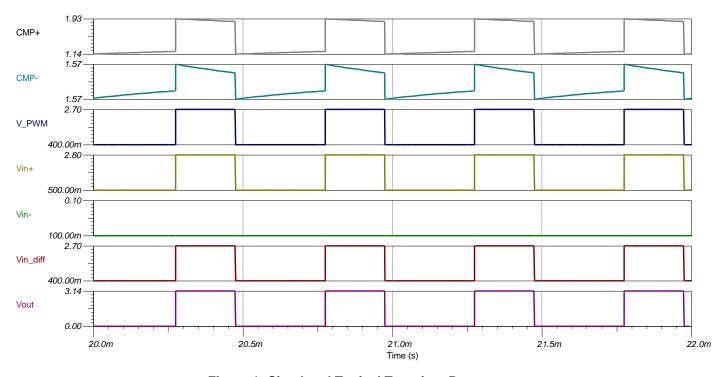

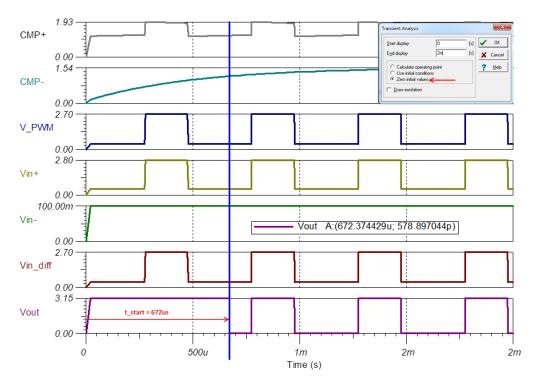

The design goals and performance are summarized in Table . Figure 1 depicts the simulated typical transient response of the design.

Table 2. Comparison of Design Goals and Simulated Performance

|                 | Goal    | Simulated  |

|-----------------|---------|------------|

| No Input Signal | Vout=0V | Vout=282pV |

| Start-up Time   | <1ms    | 672us      |

|            |           |       |       |        | Input |            | Simulated  |           |

|------------|-----------|-------|-------|--------|-------|------------|------------|-----------|

| Worst Case | Input     | Input | Input | Input  | Duty  | Comparator | Vout       | Simulated |

| Test Case  | Frequency | VIL   | VIH   | VCM    | Cycle | Vcc        | Duty Cycle | Delay     |

| 1          | 2kHz      | 0V    | 5.25V | +100mV | 40%   | 3.135V     | 40%        | 0ns       |

| 2          | 2kHz      | 400mV | 2.7V  | +100mV | 40%   | 3.135V     | 40%        | 0ns       |

|            |           |       |       |        |       |            |            |           |

| 3          | 2kHz      | 0V    | 5.25V | -100mV | 40%   | 3.135V     | 40%        | 0ns       |

| 4          | 2kHz      | 400mV | 2.7V  | -100mV | 40%   | 3.135V     | 40%        | 0ns       |

|            |           |       |       |        |       |            |            |           |

| 5          | 32MHz     | 0V    | 5.25V | +100mV | 40%   | 3.135V     | 57%        | 3.6ns     |

| 6          | 32MHz     | 400mV | 2.7V  | +100mV | 40%   | 3.135V     | 52%        | 3.6ns     |

|            |           |       |       |        |       |            |            |           |

| 7          | 32MHz     | 0V    | 5.25V | -100mV | 40%   | 3.135V     | 57%        | 3.6ns     |

| 8          | 32MHz     | 400mV | 2.7V  | -100mV | 40%   | 3.135V     | 51%        | 3.6ns     |

Figure 1: Simulated Typical Transient Response

# 2 Theory of Operation

#### Design Analysis:

- Use low est value resistors possible for 32MHz inputs.

Resistors will interact with comparator parasitic input capacitance

- 2) Set Vin- to mid-supply bias point

- 3) Set Vin+ < mid-supply + Vos to ensure at no signal Vout=0V

- 4) In addition, the signal needs to divided down with R3 to prevent negative voltages for 0-5V inputs.

#### Design Analysis:

- 5) AC Couple, High pass frequency:

- Large capacitors require longer startup time from pow er-on. Use 1uF to get high pass of about 162Hz.

- For high pass equivalent Cin = 0.5uF, Rin = 1.964k.

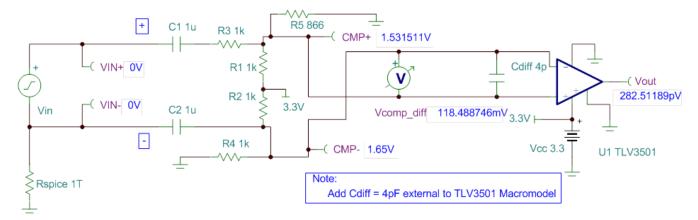

Figure 2: Complete Circuit Schematic

# 3 Component Selection

## 3.1 Comparator Selection

From Table 1 we see the minimum  $t_{ON}$  of 12.5ns is at 32MHz, 40% duty cycle. If our comparator has a propagation delay any longer than 12.5ns we will not detect a 32MHz signal of 40% duty cycle.

Table 3 highlights the key comparator specifications as single supply (2.5V to 3.5V), rail-to-rail input and propagation delay less than or equal to 12.5ns based on the maximum input frequency of 32MHz with a 40% duty cycle. The TLV3501 meets all of these criteria.

**Table 3. Comparator Specifications**

| ELECTRICAL CHARACT                                                                     |                                          |                                                                                                                                  |             |                                              |                |                                    |  |

|----------------------------------------------------------------------------------------|------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|-------------|----------------------------------------------|----------------|------------------------------------|--|

| Boldface limits apply over the s                                                       | <del></del>                              | - 7                                                                                                                              | 125°C.      |                                              |                |                                    |  |

| At $T_A = +25^{\circ}C$ and $V_S = +2.7V$ to +5                                        | 5.5V, unless other                       | erwise noted.                                                                                                                    |             |                                              |                |                                    |  |

|                                                                                        |                                          |                                                                                                                                  | TL          | TLV3501, TLV3502                             |                |                                    |  |

| PARAMETER                                                                              |                                          | CONDITION                                                                                                                        | MIN         | MIN TYP MAX                                  |                |                                    |  |

| OFFSET VOLTAGE Input Offset Voltage(1) vs Temperature vs Power Supply Input Hysteresis | VOS<br>dVOS/dT<br>PSRR                   | V <sub>CM</sub> = 0V, I <sub>O</sub> = 0mA<br>T <sub>A</sub> = -40°C to +125°C<br>V <sub>S</sub> = 2.7V to 5.5V                  |             | ±1<br>±5<br>100<br>6                         | ±6.5<br>400    | m∨<br>μ <b>V</b> /°C<br>μ∨/∨<br>m∨ |  |

| INPUT BIAS CURRENT<br>Input Bias Current<br>Input Offset Current(2)                    | I <sub>B</sub>                           | V <sub>CM</sub> = V <sub>CC</sub> /2<br>V <sub>CM</sub> = V <sub>CC</sub> /2                                                     |             | ±2<br>±2                                     | ±10<br>±10     | pA<br>pA                           |  |

| INPUT VOLTAGE RANGE                                                                    |                                          |                                                                                                                                  |             |                                              |                |                                    |  |

| Common-Mode Voltage Range                                                              | VCM                                      |                                                                                                                                  | (V-) - 0.2V |                                              | (V+) + 0.2V    | V                                  |  |

| Common-Mode Rejection                                                                  | CMRR                                     | $V_{CM} = -0.2V \text{ to } (V+) + 0.2V$<br>$V_{CM} = -0.2V \text{ to } (V+) + 0.2V$                                             | 57<br>55    | 70                                           |                | dB<br>dB                           |  |

| INPUT IMPEDANCE<br>Common-Mode<br>Differential                                         |                                          |                                                                                                                                  |             | 10 <sup>13</sup>   2<br>10 <sup>13</sup>   4 |                | Ω   pi                             |  |

| SWITCHING CHARACTERISTICS                                                              | ;                                        |                                                                                                                                  |             |                                              |                |                                    |  |

| Propagation Delay Time <sup>(3)</sup>                                                  | T <sub>(pd)</sub>                        | $\Delta V_{IN}$ = 100mV, Overdrive = 20m<br>$\Delta V_{IN}$ = 100mV, Overdrive = 20m<br>$\Delta V_{IN}$ = 100mV, Overdrive = 5mV | ١V          | 4.5<br>7.5                                   | 6.4<br>7<br>10 | ns<br>ns<br>ns                     |  |

| Propagation Delay Skew(4)                                                              | ∆t(SKEW)                                 | $\Delta V_{IN}$ = 100mV, Overdrive = 5m $\Delta V_{IN}$ = 100mV, Overdrive = 20m                                                 | V           | 0.5                                          | 12             | ns<br>ns<br>MHz                    |  |

| Maximum Toggle Frequency<br>Rise Time(5)<br>Fall Time(5)                               | fMAX<br>t <sub>R</sub><br>t <sub>F</sub> | Overdrive = 50mV, V <sub>S</sub> = 5V                                                                                            |             | 80<br>1.5<br>1.5                             |                | ns<br>ns                           |  |

| OUTPUT<br>Voltage Output from Rail                                                     | VOH, VOL                                 | I <sub>OUT</sub> = ±1mA                                                                                                          |             | 30                                           | 50             | m∨                                 |  |

# 3.2 Comparator Input Capacitance and Low Pass Frequency

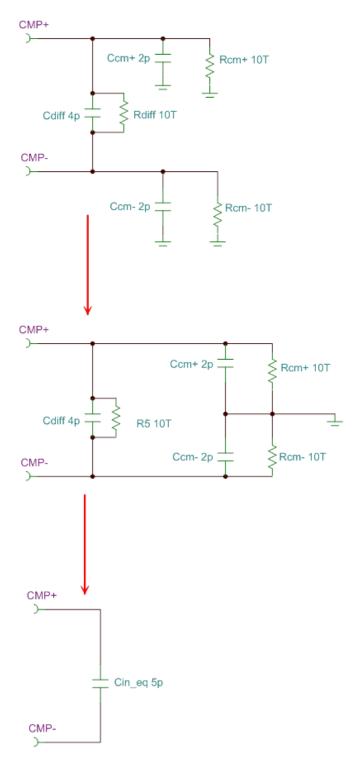

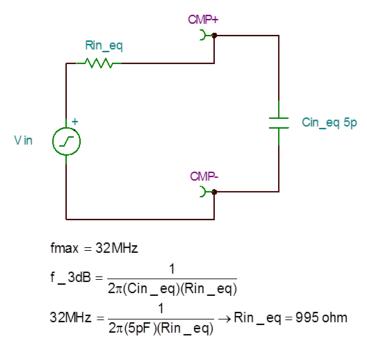

Figure 3 is the equivalent input impedance of the TLV3501 comparator. Through series and parallel combination of the input capacitances we can arrive at the total equivalent differential input capacitance, Cin\_eq, of 5pF.

Figure 3: Comparator Input Capacitance

The total equivalent input capacitance, Ceq\_in, combined with the total input resistance, Rin\_eq, will form a single pole which will attenuate the input signal. Since our maximum input frequency is 32MHz we will choose a low pass frequency point no lower than this. As shown in Figure 4 we will need to limit Rin\_eq to less than or equal to 995 ohms.

Figure 4: Low Pass Filter Limitations

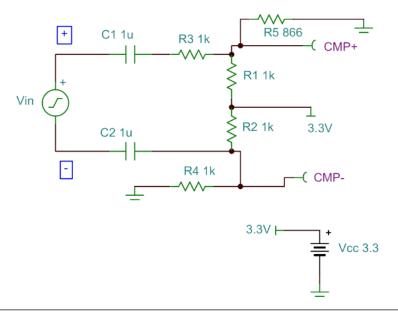

## 3.3 Input Scaling Offset

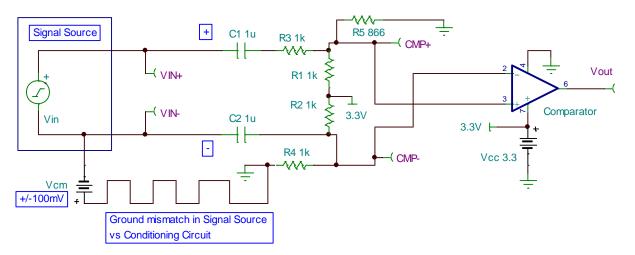

The input scaling offset circuit consists of R1, R2, R4, R5 and the supply voltage Vcc, as shown in Figure 5. The offset is computed for dc with no dynamic input signal. R2 and R4 divide Vcc to give CMP- a 1.65V offset. R1 and R5 divide down Vcc to yield a 1.53V offset on CMP+. Through the use of standard values CMP+ is about 100mV lower than CMP-. This ensures that with the TLV3501 input offset voltage of +/-6.5mV plus room for noise margin we will have the TLV3501 output forced to zero when no signal is present, as required by our design specifications.

- 1) Offset both inputs to mid-supply so Vin negative voltages will be offset to a positive value to meet TLV3501common mode voltage range.

- 2) Set CMP- > (CMP+) + 100mV to ensure with Vin=0V TLV3501 Output = 0V.

- 3) From Figure 4 we know Rin eq = 995 ohms to allow Vin to pass due to TLV3501 input capacitance.

- 4) Start by using 1k range values to yield Rin eq = 995 ohms.

- 5) On CMP- use standard values and set R2=R4=1k for Vcm=Vcc/2

- 6) On CMP+ use standard values and set CMP+ < (CMP-) 100mV.

Set R1=1k to keep near matched resistance from Vcc to GND. Select R5 for offset from CMP-.

Figure 5: Input Scaling Offset

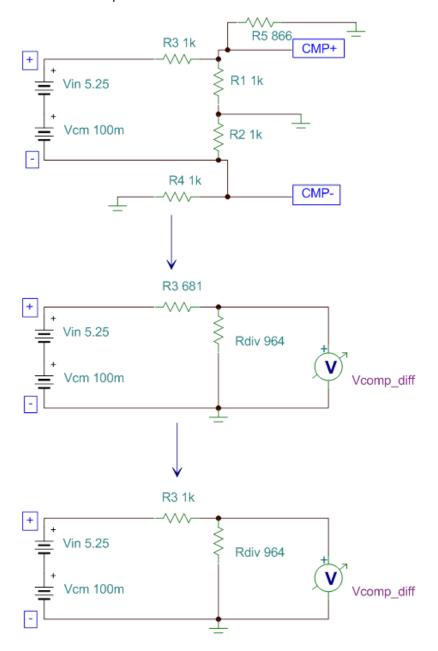

## 3.4 Input Divider

Once the Vin signal is ac coupled into our comparator circuit, we need to ensure its amplitude is no larger than the minimum input common mode voltage range of the TLV3501. Figure 6 details our analysis for choosing the last scaling resistor, R3, to adequately divide down the maximum Vin amplitude to within our minimum common mode input of the TLV3501.

- 1) Vin\_max = 5.25V + 100mV.

- 2) Equivalent resistor network in series with R3 is 964 ohms.

- 3) Minimum Vcc = 3.135V

- 4) Keep Vcomp\_diff < 3.135V to meet Vcm specification of TLV3901.

- 5) R3\_min = 681 ohms. Choose R3=1k for better margin and standard value already used.

Figure 6: Input Divider

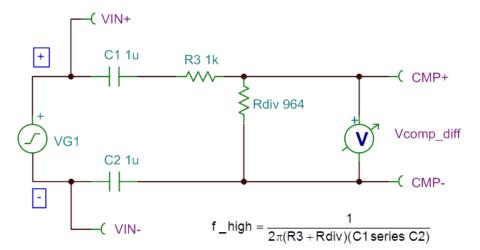

## 3.5 Input High Pass Filter

The ac coupling of Vin into our comparator is set by R3, Rdiv, C1 and C2 as detailed in Figure 7.

- 1)  $fin_min = 2kHz$

- 2) Set f\_high < 200Hz. At least one decade under desired pass frequency for high pass cut frequency.

- 3) For standard capacitor value set C1=C2 = 1uF.

- 4) f\_high calculates as 162Hz.

Figure 7: Input High Pass Filter

## 3.6 Recommend Component Properties

Table 4 gives recommended component properties for the parts used in the AC Coupled Comparator circuit.

**Table 4. Recommended Component Properties**

| Ref Designator | Value   | Recommended Properties                                             |

|----------------|---------|--------------------------------------------------------------------|

| C1, C2         | 1uF     | 10%, Ceramic Capacitor, X5R or X7R tempco                          |

| R1, R2, R3, R4 | 1k ohm  | 1/8W, 1% Film Resistor, 100ppm tempco                              |

| R5             | 866 ohm | 1/8W, 1% Film Resistor, 100ppm tempco                              |

| U1             | TLV3501 | Single Supply, +2.7V to +5.5V, Cin < 5pF, Propogation Delay < 12ns |

#### 4 Simulation

## 4.1 Input Scaling Frequency Check

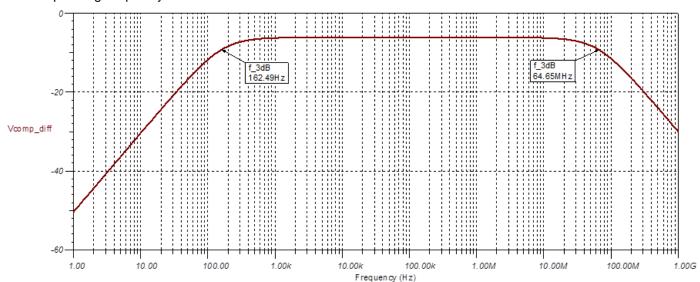

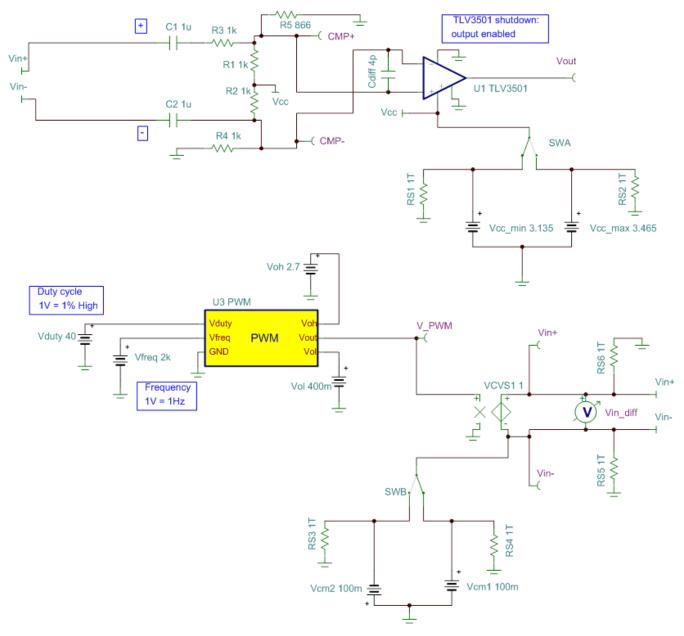

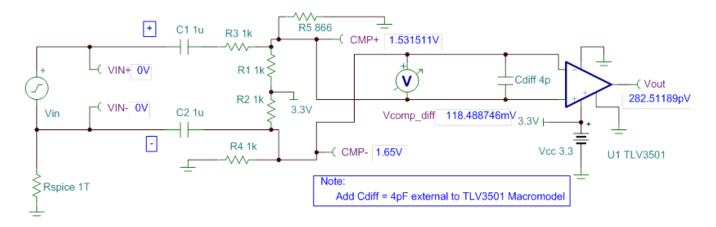

The circuit in Figure 8 allows us to check the frequency response of the input scaling network. We have added an additional 4pF of differential input capacitance, Cdiff, to the TLV3501 in Figure 8 to properly model the complete input capacitance of the comparator. See Appendix A for details on this modification.

Figure 8: Input Scaling Frequency Test Circuit

From Figure 9, we see that the input scaling network will pass signals between the -3dB high-pass point of 162Hz to the low pass cut-off frequency of 64MHz. The 162Hz is about one decade away from our specified low frequency signal range of 2KHz. The 64MHz low pass is about twice our upper specified operating frequency of 32MHz.

Figure 9: Input Scaling Frequency Response

# 4.2 AC Coupled Signals Yield Negative Voltages

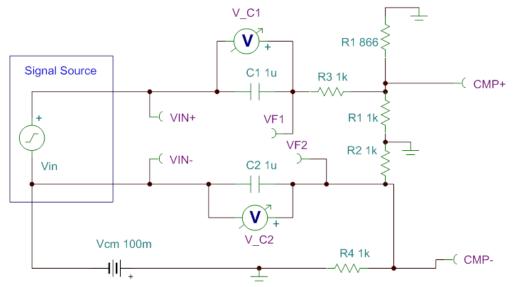

If we remove our dc offset voltage of Vcc=3.3V, as shown in the test circuit of Figure 10, we can see the effects of ac coupling and the magnitudes of negative voltages that would appear at the TLV3501 inputs, CMP+ and CMP-. From superposition, whatever negative voltages that appear will be counteracted directly by our positive dc offsets of 1.65V on CMP- and 1.53V on CMP-. Figure 11 and Figure 12 show that we do indeed need our dc offsets on CMP+ and CMP-.

Figure 10: AC Coupled Signals - Negative Voltage Test

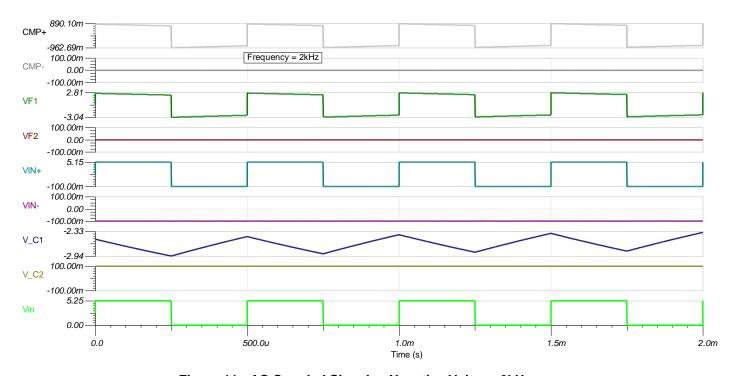

Figure 11: AC Coupled Signals - Negative Voltage 2kHz

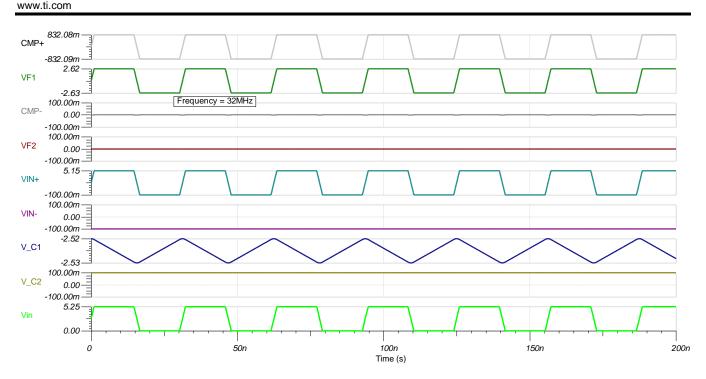

Figure 12: AC Coupled Signals - Negative Voltage 32MHz

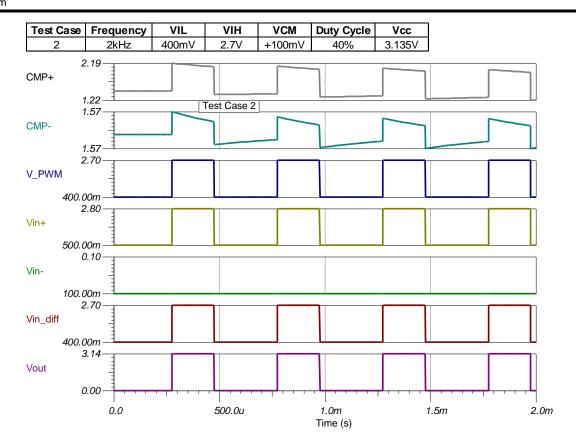

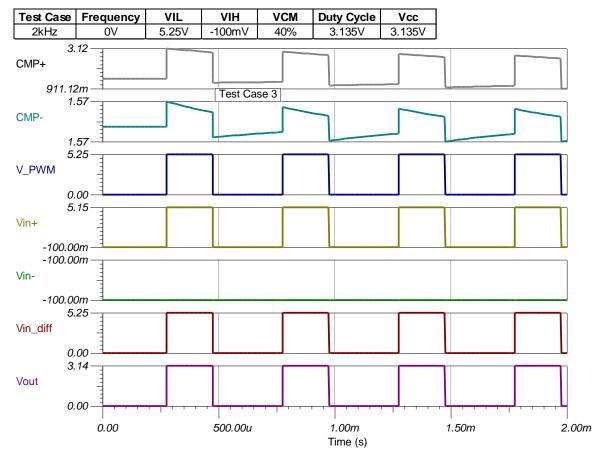

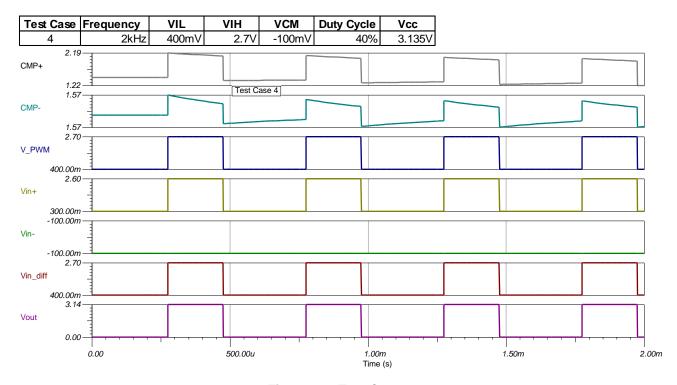

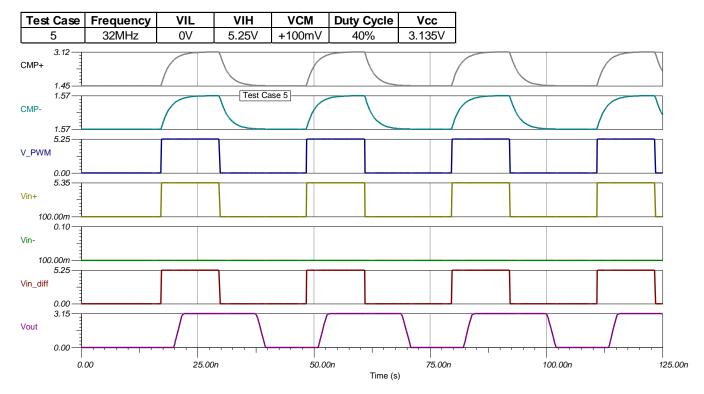

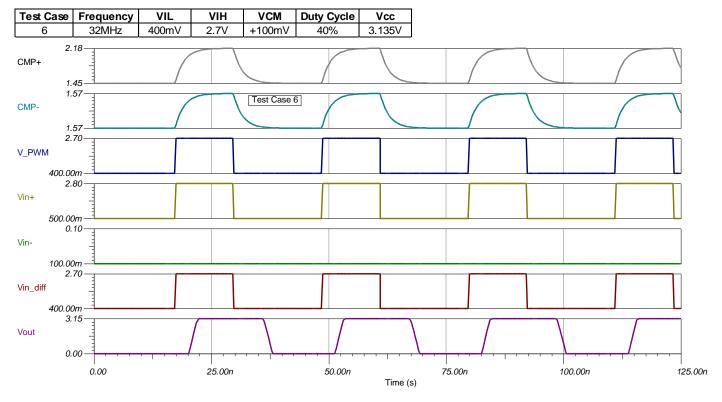

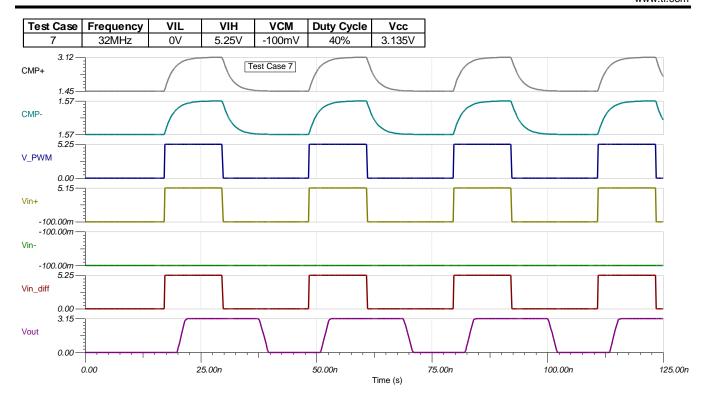

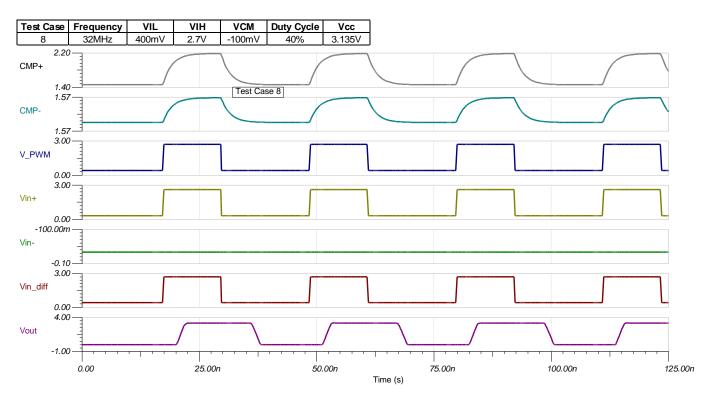

#### 4.3 Test Cases

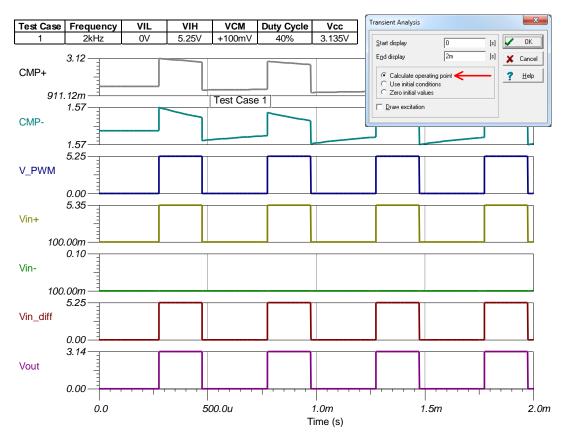

The worst case test cases for our design are detailed in Table 5. To ensure the circuit works robustly at the extremes, minimum and maximum input amplitudes are checked along with minimum and maximum frequencies and minimum and maximum common mode input voltage. Figure 13 is the test circuit for checking our final design. Figure 14 shows the initial start-up time until reliable signals will be seen out of the TLV3501. By selecting "Zero Initial Values" in the Transient Analysis control window we can see how long it takes for the input AC coupling capacitors to charge resulting in reliable pulses out after about 672 microseconds. For Figure 15 through Figure 22 we set "Calculate Operating Point" in the Transient Analysis control window so we will ignore the start-up time and see the behavior of our circuit after C1 and C2 are past the initial start-up. The key thing we need to look at is how far CMP+ is swinging about CMP-. Input offset voltage for the TLV3501 comparator is +/-6.5mV. We want to stay way away from this in our high and low AC coupled input levels for reliable operation. In all test cases CMP+ is at least 120mV above or below CMP- in the high and low levels AC coupled into the TLV3501 comparator inputs.

**Table 5. Worst Case Test Cases**

| Worst Case Test Cases for AC Coupled Comparator |           |       |       |        |                   |        |  |  |  |

|-------------------------------------------------|-----------|-------|-------|--------|-------------------|--------|--|--|--|

|                                                 |           |       |       |        |                   |        |  |  |  |

| Test Case                                       | Frequency | VIL   | VIH   | VCM    | <b>Duty Cycle</b> | Vcc    |  |  |  |

| 1                                               | 2kHz      | 0V    | 5.25V | +100mV | 40%               | 3.135V |  |  |  |

| 2                                               | 2kHz      | 400mV | 2.7V  | +100mV | 40%               | 3.135V |  |  |  |

|                                                 |           |       |       |        |                   |        |  |  |  |

| 3                                               | 2kHz      | 0V    | 5.25V | -100mV | 40%               | 3.135V |  |  |  |

| 4                                               | 2kHz      | 400mV | 2.7V  | -100mV | 40%               | 3.135V |  |  |  |

|                                                 |           |       |       |        |                   |        |  |  |  |

| 5                                               | 32MHz     | 0V    | 5.25V | +100mV | 40%               | 3.135V |  |  |  |

| 6                                               | 32MHz     | 400mV | 2.7V  | +100mV | 40%               | 3.135V |  |  |  |

|                                                 |           |       |       |        |                   |        |  |  |  |

| 7                                               | 32MHz     | 0V    | 5.25V | -100mV | 40%               | 3.135V |  |  |  |

| 8                                               | 32MHz     | 400mV | 2.7V  | -100mV | 40%               | 3.135V |  |  |  |

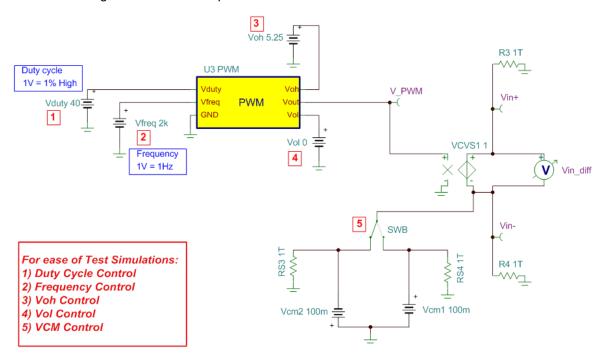

To test our final design we will use an easy to adjust PWM signal generator as shown in Figure 13. This generator has adjustable frequency, duty cycle, Voh (output high voltage level), and Vol (output high voltage level). This allows us to easily test all corner conditions of our specification for our final circuit implementation compliance. Refer to Appendix B for design details of the PWM Signal Source. In addition we will add two common mode voltages, Vcm1 (+100mV) or Vcm2 (-100mV) to offset our PWM signal generator on the output of VCVS1 (voltage-controlled-voltage source) per our Vin common mode specification. A switch, SWB, will select our common mode input applied voltage. Note that both common mode voltages have a 1T ohm resistor in parallel with them t avoid SPICE convergence issues. The outputs of VCVS1 are each terminated with 1T ohm resistors for SPICE convergence when we connect to our ac coupled comparator inputs.

Figure 13: SPICE Test Case Circuit

Figure 14: Initial Start Charge Time for CMP-

Figure 15: Test Case 1

Figure 16: Test Case 2

Figure 17: Test Case 3

Figure 18: Test Case 4

Figure 19: Test Case 5

Figure 20: Test Case 6

Figure 21: Test Case 7

Figure 22: Test Case 8

#### 5 Modifications

The components selected for this design were based on the design goals outlined at the beginning of the design process. Selecting a short propagation delay comparator such as the TLV3501 is critical in achieving the upper operating frequency of 32MHz. Initial tolerances and temperature coefficient of C1 and C2 should be analyzed for their effects on voltages coupled into the comparator inputs. Ensure all voltages remain within the common mode voltage range of the selected comparator. By using cut frequencies a decade away from the desired pass band frequencies, component sensitivities are minimized. Based on a minimum duty cycle of 40% and single supply operation from 2.7V < Vcc < 5.5V, Table 6 lists the maximum frequency possible, based on propagation delay, for rail to rail input comparators which are optimal for this type of design.

Table 6. Single Supply Comparators and Maximum Frequency for AC Coupled Comparator

| Part    | RRI | Channels | Vcc Min | Vcc Max | Output Type        | Iq/Channel | Prop Delay | fmax       |

|---------|-----|----------|---------|---------|--------------------|------------|------------|------------|

|         |     |          | (V)     | (V)     |                    | (mA)       | (us)       | (Hz)       |

| TLV3404 | Yes | 4        | 2.5     | 16      | open drain         | 0.00095    | 300        | 1,333      |

| TLV3402 | Yes | 2        | 2.5     | 16      | open drain         | 0.00095    | 300        | 1,333      |

| TLV3401 | Yes | 1        | 2.5     | 16      | open drain         | 0.00095    | 300        | 1,333      |

| TLV3704 | Yes | 4        | 2.7     | 16      | push/pull          | 0.001      | 240        | 1,667      |

| TLV3702 | Yes | 2        | 2.7     | 16      | push/pull          | 0.001      | 240        | 1,667      |

| TLV3701 | Yes | 1        | 2.7     | 16      | push/pull          | 0.001      | 240        | 1,667      |

| LMC7225 | Yes | 1        | 2       | 8       | open dra <i>in</i> | 1.2        | 29         | 13,793     |

| LMC7215 | Yes | 1        | 2       | 8       | push/pull          | 1.2        | 29         | 13,793     |

| TLV3494 | Yes | 4        | 1.8     | 5.5     | push/pull          | 0.0012     | 13.5       | 29,630     |

| TLV3492 | Yes | 2        | 1.8     | 5.5     | push/pull          | 0.0012     | 13.5       | 29,630     |

| TLV3491 | Yes | 1        | 1.8     | 5.5     | push/pull          | 0.0012     | 13.5       | 29,630     |

| LPV7215 | Yes | 1        | 1.8     | 5.5     | push/pull          | 0.013      | 12         | 33,333     |

| TLV7211 | Yes | 1        | 2.7     | 15      | push/pull          | 0.014      | 10         | 40,000     |

| LMC7221 | Yes | 1        | 2.7     | 15      | open drain         | 0.018      | 10         | 40,000     |

| LMC7211 | Yes | 1        | 2.7     | 15      | push/pull          | 0.014      | 10         | 40,000     |

| LMC6762 | Yes | 2        | 2.7     | 15      | push/pull          | 12.5       | 10         | 40,000     |

| LMV7291 | Yes | 1        | 1.8     | 5.5     | push/pull          | 0.016      | 1.3        | 307,692    |

| LMV762  | Yes | 2        | 2.7     | 5.25    | push/pull          | 0.7        | 0.27       | 1,481,481  |

| LMV761  | Yes | 1        | 2.7     | 5.25    | push/pull          | 0.7        | 0.27       | 1,481,481  |

| LMV7239 | Yes | 1        | 2.7     | 5.5     | push/pull          | 0.1        | 0.096      | 4,166,667  |

| LMV7235 | Yes | 1        | 2.7     | 5.5     | open drain         | 0.1        | 0.096      | 4,166,667  |

| TLV3502 | Yes | 2        | 2.7     | 5.5     | push/pull          | 5          | 0.012      | 33,333,333 |

| TLV3501 | Yes | 1        | 2.7     | 5.5     | push/pull          | 5          | 0.012      | 33,333,333 |

<sup>\*</sup>fmax based on 40% duty cycle

### 6 About the Author

After earning a BSEE from the University of Arizona, in 1981, Tim Green has worked as an analog and mixed signal board/system design engineer, strategic marketing engineer, and linear applications engineer, for over 31 years. Product areas he has focused on are brushless motor control, aircraft jet engine control, missile systems, power op amps, data acquisition systems, CCD cameras, and analog/mixed signal semiconductors. Tim's most recent experience focused on Power Audio for the automotive market. He is currently a Senior Analog Applications Engineer in Precision Analog Linear Applications at Texas Instruments Inc, Tucson Design Center.

# Appendix A.

## A.1 TLV3501 Input Capacitance Test

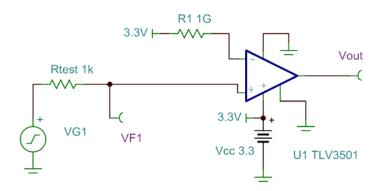

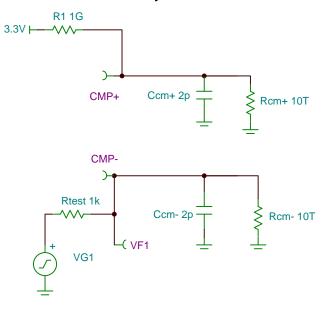

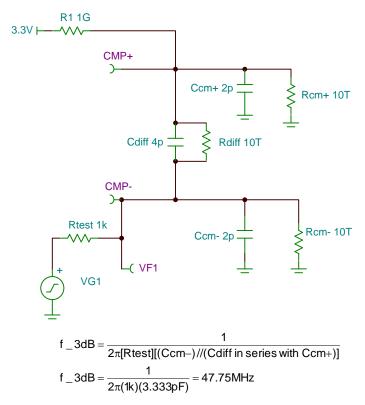

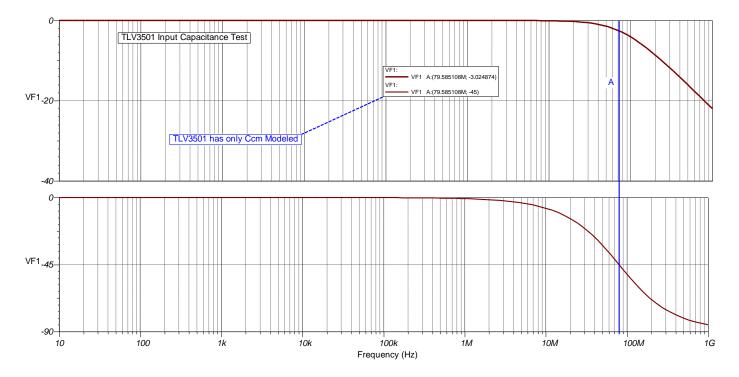

Since a critical part of our design specification is high frequency operation, we will check that the TLV3501 SPICE macromodel matches the data sheet specifications for Ccm and Cdiff. Figure A-1 shows a simple test circuit in which we sweep an ac source through a known resistance, Rtest, and look at the 3dB frequency caused by this known resistance and the input capacitance of the SPICE macromodel. In Figure A-2 we compute the expected results of our test if just Ccm is modeled or if both Ccm and Cdiff are modeled. From Figure A-3, the results of our SPICE simulation, we see that only Ccm seems to be modeled in the TLV3501 SPICE macromodel. To make sure our design works robustly in the real world we will add Cdiff of 4pF external to the TLV3501 SPICE macromodel as shown in Figure A-4.

Figure A-1: TLV3501 Input Capacitance Test Circuit

## If TLV3501 has only Ccm Modeled

$$f_3dB = \frac{1}{2\pi(Rtest)(Ccm-)}$$

$f_3dB = \frac{1}{2\pi(1k)(2pF)} = 79.58MHz$

## If TLV3501 has Ccm and Cdiff Modeled

Figure A-2: TLV3501 Input Capacitance Check

Figure A-3: TLV3501 Input Capacitance Simulation Results

Figure A-4: Modified TLV3501 Comparator for Proper Input Capacitance

# Appendix B.

## **B.1 Adjustable PWM Signal Source**

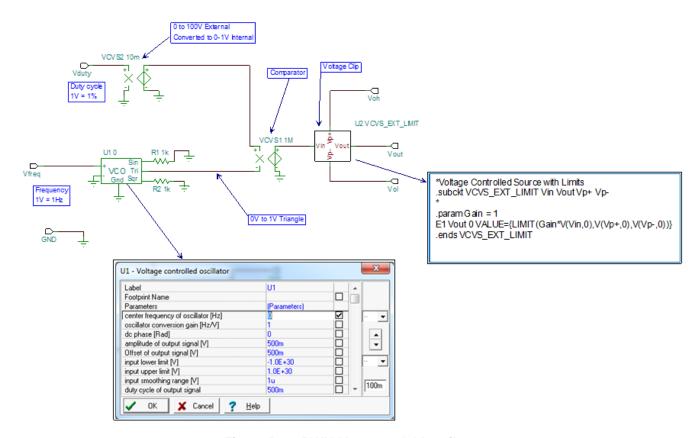

To test our final design we will create an easy to adjust and use PWM signal generator shown in Figure B-1. This generator has adjustable frequency, duty cycle, Voh (output high voltage level), and Vol (output high voltage level). This will allow us to easily test all corner conditions of our specification for our final circuit implementation compliance. Figure B-2 shows the subcircuits used inside of the PWM Macromodel. VCO is a SPICE standard voltage-controlled-oscillator out of which we will use the triangle wave output scaled for 0V to 1V. Frequency is scaled for 1V=1Hz. External to the macromodel, duty cycle is scaled 0V to 100V for 0% to 100% respectively. Internally we scale this from 0 to 1V by VCVS2. An ideal comparator, VCVS1, compares the triangle waveform (0V to 1V) to the duty cycle setting (0V to 1V). The output high and low limits, Voh and Vol, are set externally and become the limit values of U2, a voltage-controlled-voltage source with clamp limits.

Figure B-1: Transient Analysis PWM Source

Figure B-2: PWM Macromodel Details

#### IMPORTANT NOTICE FOR TI REFERENCE DESIGNS

Texas Instruments Incorporated ("TI") reference designs are solely intended to assist designers ("Buyers") who are developing systems that incorporate TI semiconductor products (also referred to herein as "components"). Buyer understands and agrees that Buyer remains responsible for using its independent analysis, evaluation and judgment in designing Buyer's systems and products.

TI reference designs have been created using standard laboratory conditions and engineering practices. TI has not conducted any testing other than that specifically described in the published documentation for a particular reference design. TI may make corrections, enhancements, improvements and other changes to its reference designs.

Buyers are authorized to use TI reference designs with the TI component(s) identified in each particular reference design and to modify the reference design in the development of their end products. HOWEVER, NO OTHER LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE TO ANY OTHER TI INTELLECTUAL PROPERTY RIGHT, AND NO LICENSE TO ANY THIRD PARTY TECHNOLOGY OR INTELLECTUAL PROPERTY RIGHT, IS GRANTED HEREIN, including but not limited to any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services, or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

TI REFERENCE DESIGNS ARE PROVIDED "AS IS". TI MAKES NO WARRANTIES OR REPRESENTATIONS WITH REGARD TO THE REFERENCE DESIGNS OR USE OF THE REFERENCE DESIGNS, EXPRESS, IMPLIED OR STATUTORY, INCLUDING ACCURACY OR COMPLETENESS. TI DISCLAIMS ANY WARRANTY OF TITLE AND ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, QUIET ENJOYMENT, QUIET POSSESSION, AND NON-INFRINGEMENT OF ANY THIRD PARTY INTELLECTUAL PROPERTY RIGHTS WITH REGARD TO TI REFERENCE DESIGNS OR USE THEREOF. TI SHALL NOT BE LIABLE FOR AND SHALL NOT DEFEND OR INDEMNIFY BUYERS AGAINST ANY THIRD PARTY INFRINGEMENT CLAIM THAT RELATES TO OR IS BASED ON A COMBINATION OF COMPONENTS PROVIDED IN A TI REFERENCE DESIGN. IN NO EVENT SHALL TI BE LIABLE FOR ANY ACTUAL, SPECIAL, INCIDENTAL, CONSEQUENTIAL OR INDIRECT DAMAGES, HOWEVER CAUSED, ON ANY THEORY OF LIABILITY AND WHETHER OR NOT TI HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES, ARISING IN ANY WAY OUT OF TI REFERENCE DESIGNS OR BUYER'S USE OF TI REFERENCE DESIGNS.

TI reserves the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques for TI components are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

Reproduction of significant portions of TI information in TI data books, data sheets or reference designs is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards that anticipate dangerous failures, monitor failures and their consequences, lessen the likelihood of dangerous failures and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in Buyer's safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed an agreement specifically governing such use.

Only those TI components that TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components that have *not* been so designated is solely at Buyer's risk, and Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of non-designated products, TI will not be responsible for any failure to meet ISO/TS16949.