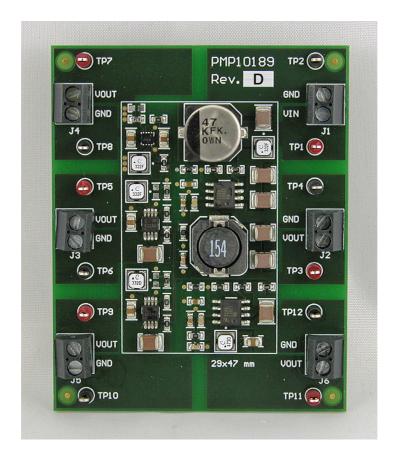

# **Hercules Safety MCU Power Solution**

• Input 48..60V DC

• Outputs

LM5017 +12.0V @ 515mA

TPS62160 +5.0V @ 430mA

TLV62080 +1.2V @ 700mA

TPS62160 +3.3V @ 620mA

LM5017 +3.3V @ 230mA

## 1 LM5017 - +12.0V @ 515mA

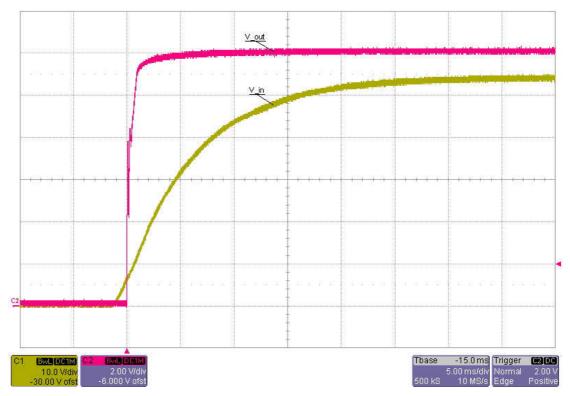

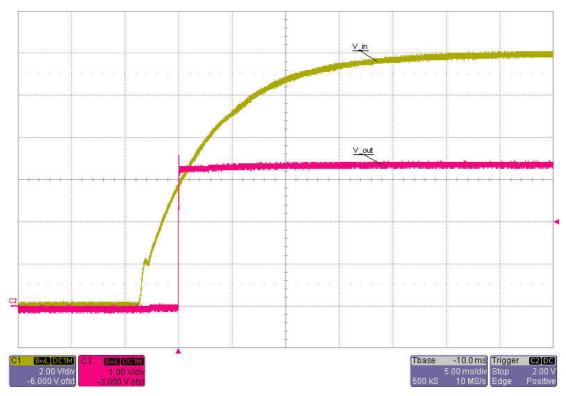

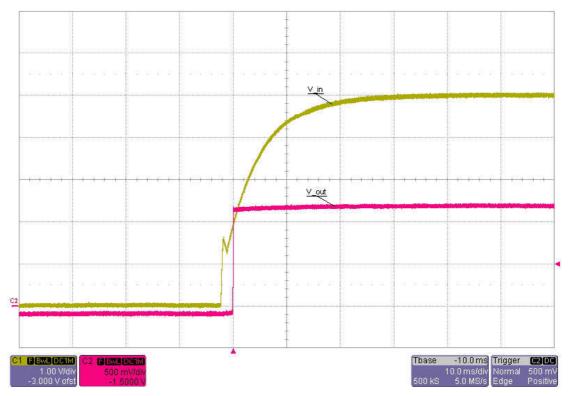

### 1.1 Startup

The startup waveform is shown in Figure 1. The input voltage is set at 54.0V with no load on the 12.0V output.

Channel C1: **54.0V Input voltage**

10V/div, 5ms/div

Channel C2: 12.0V Output voltage

Figure 1

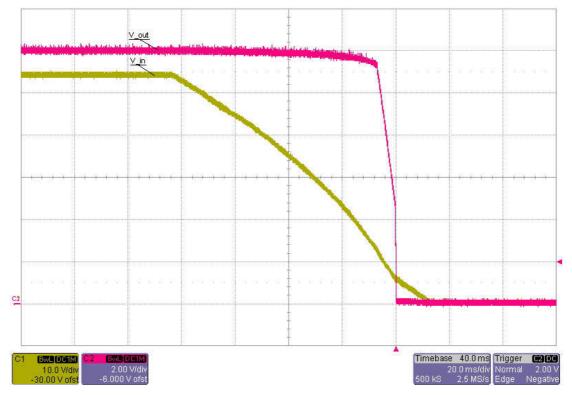

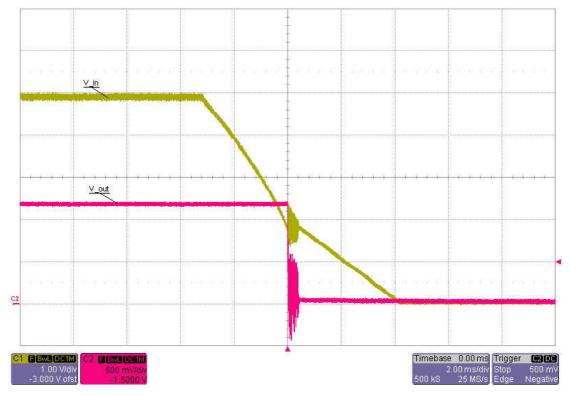

### 1.2 Shutdown

The shutdown is shown in Figure 2. The input voltage is set at 54.0V with 515mA load on the output.

Channel C1: **54.0V Input voltage**

10V/div, 20ms/div

Channel C2: **12.0V Output voltage**

2V/div, 20ms/div

Figure 2

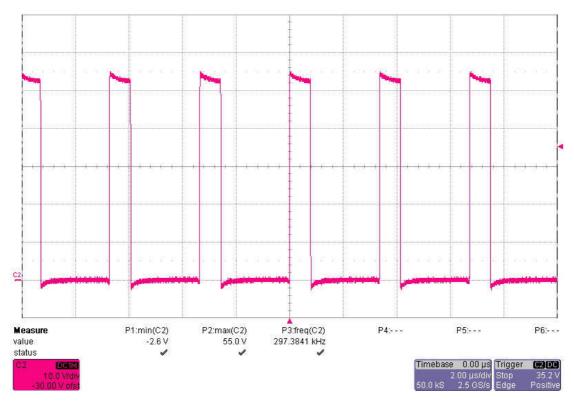

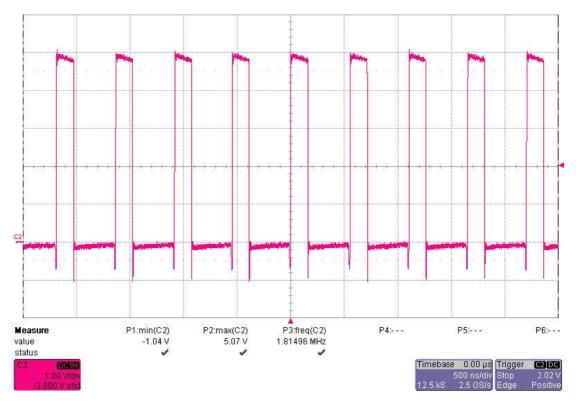

### 1.3 Switching Node

The drain-source voltage on the switching node is shown in Figure 3. The image is captured with 54V input voltage and 515mA load on the 12.0V output.

Channel C2: **Drain-source voltage**, -2.6V minimum voltage, 55.0V maximum voltage 10V/div, 2us/div

Figure 3

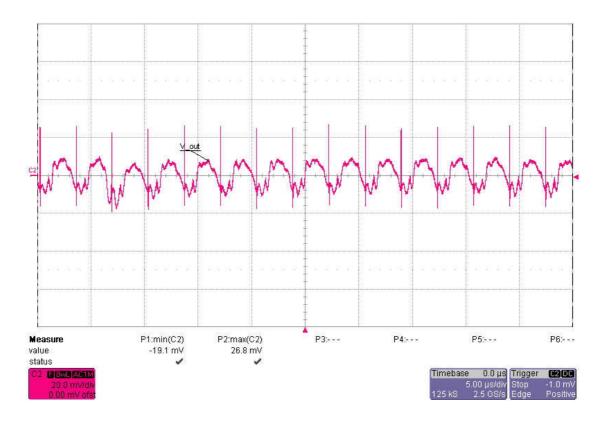

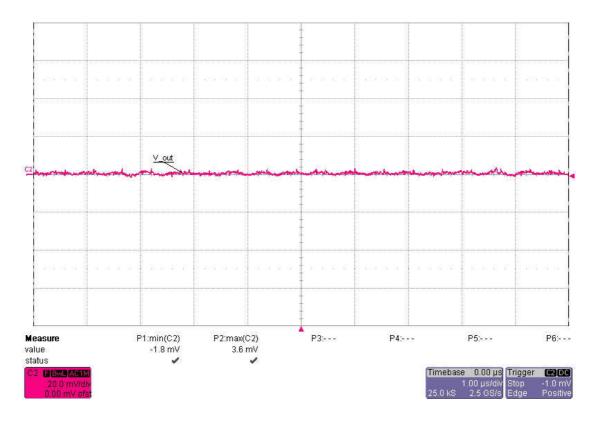

### 1.4 Output Ripple

The output ripple voltage is shown in Figure 4. The input voltage is set at 54.0V with 515mA load on the output.

Channel C2: **Output voltage** @ **54.0V input**, 22mV peak-peak (0.2%) 20mV/div, 5us/div, AC coupled

Figure 4

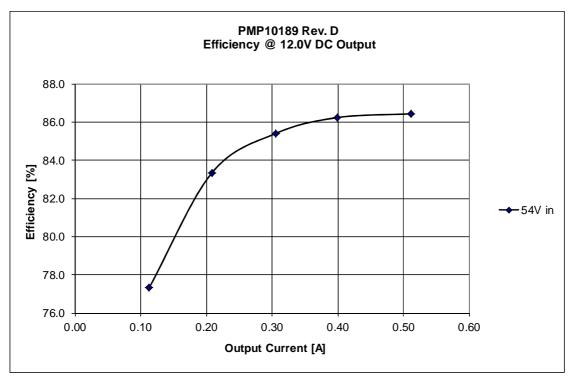

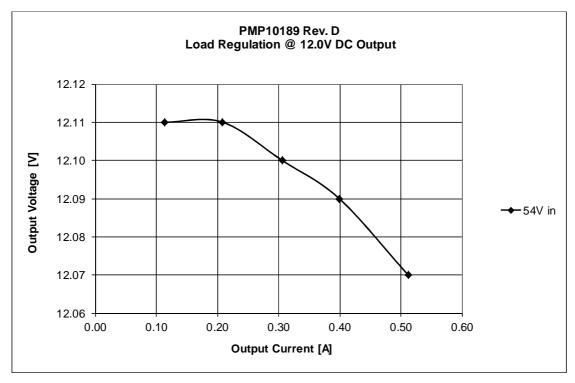

### 1.5 Efficiency & Load Regulation

The efficiency and load regulation are shown in Figure 5 and Figure 6.

Figure 5

Figure 6

## 2 LM5017 - +3.3V @ 230mA

### 2.1 Startup

The startup waveform is shown in Figure 7. The input voltage is set at 12.0V with no load on the 3.3V output.

Channel C1: **12.0V Input voltage**

2V/div, 5ms/div

Channel C2: **3.3V Output voltage**

Figure 7

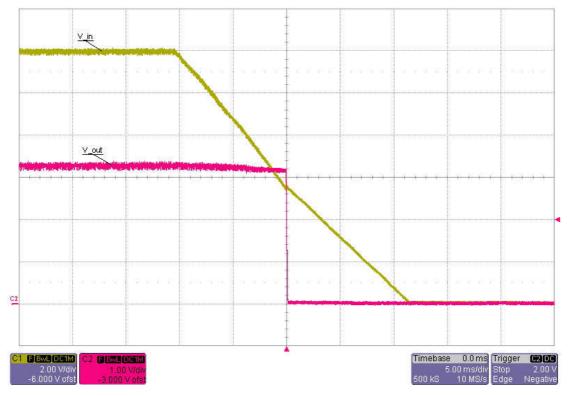

### 2.2 Shutdown

The shutdown is shown in Figure 8. The input voltage is set at 12.0V with 230mA load on the output.

Channel C1: 12.0V Input voltage

2V/div, 5ms/div

Channel C2: **3.3V Output voltage**

Figure 8

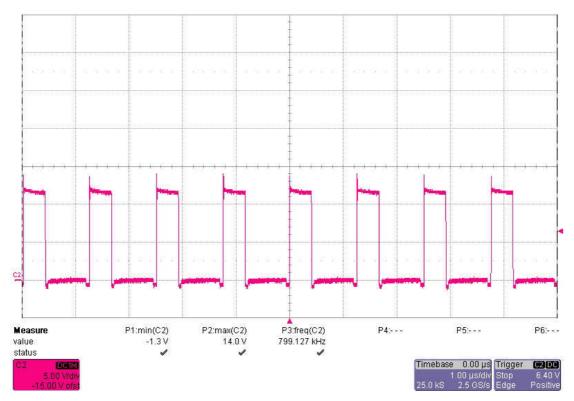

### 2.3 Switching Node

The drain-source voltage on the switching node is shown in Figure 9. The image is captured with 12V input voltage and 230mA load on the 3.3V output.

Channel C2: **Drain-source voltage**, -1.3V minimum voltage, 14.0V maximum voltage 5V/div, 1us/div

Figure 9

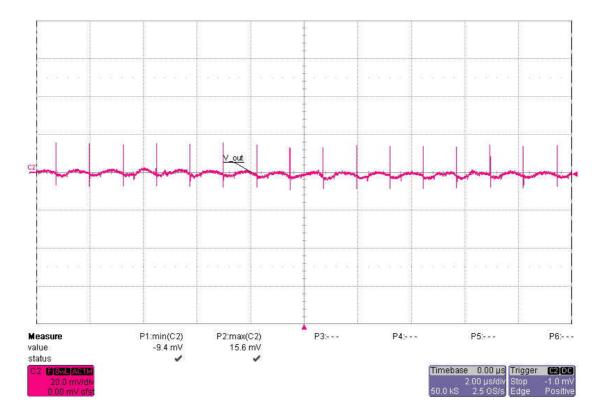

### 2.4 Output Ripple

The output ripple voltage is shown in Figure 10. The input voltage is set at 12.0V with 230mA load on the output.

Channel C2: **Output voltage @ 12.0V input**, 6mV peak-peak (0.2%) 20mV/div, 2us/div, AC coupled

Figure 10

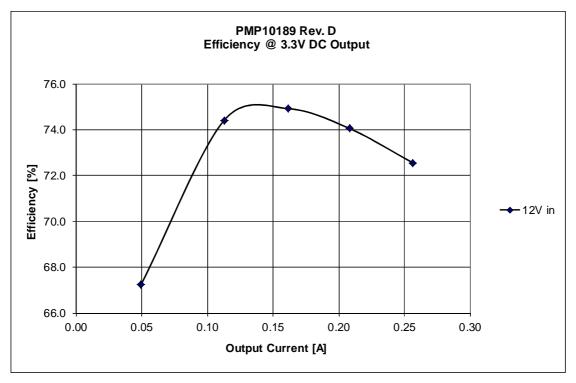

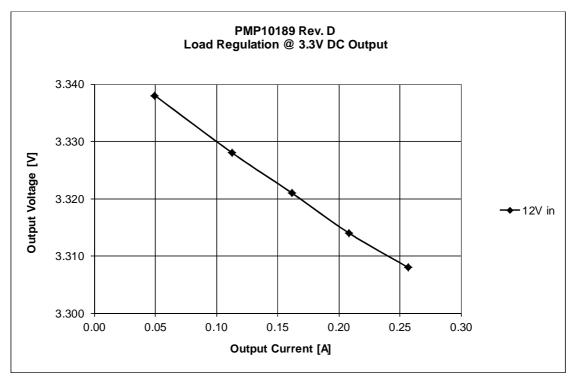

### 2.5 Efficiency & Load Regulation

The efficiency and load regulation are shown in Figure 11 and Figure 12.

Figure 11

Figure 12

## 3 TPS62160 - +5.0V @ 430mA

### 3.1 Startup

The startup waveform is shown in Figure 13. The input voltage is set at 12.0V with no load on the 5.0V output.

Channel C1: **12.0V Input voltage**

2V/div, 5ms/div

Channel C2: **5.0V Output voltage**

Figure 13

#### 3.2 Shutdown

The shutdown is shown in Figure 14. The input voltage is set at 12.0V with 430mA load on the output.

Channel C1: 12.0V Input voltage

2V/div, 5ms/div

Channel C2: **5.0V Output voltage**

Figure 14

### 3.3 Switching Node

The drain-source voltage on the switching node is shown in Figure 15. The image is captured with 12V input voltage and 430mA load on the 5.0V output.

Channel C2: **Drain-source voltage**, -1.0V minimum voltage, 13.0V maximum voltage 2V/div, 500ns/div

Figure 15

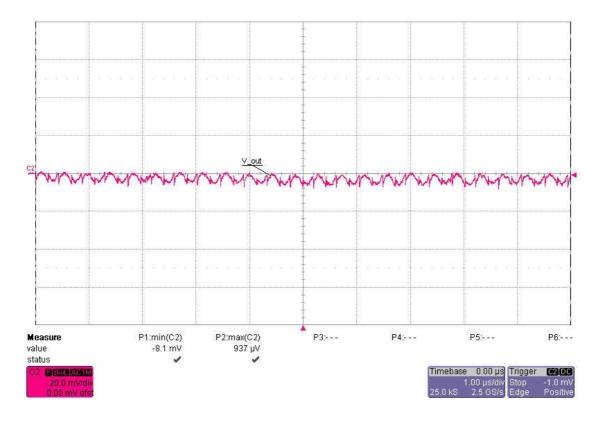

### 3.4 Output Ripple

The output ripple voltage is shown in Figure 16. The input voltage is set at 12.0V with 430mA load on the output.

Channel C2: **Output voltage @ 12.0V input**, 8mV peak-peak (0.2%) 20mV/div, 1us/div, AC coupled

Figure 16

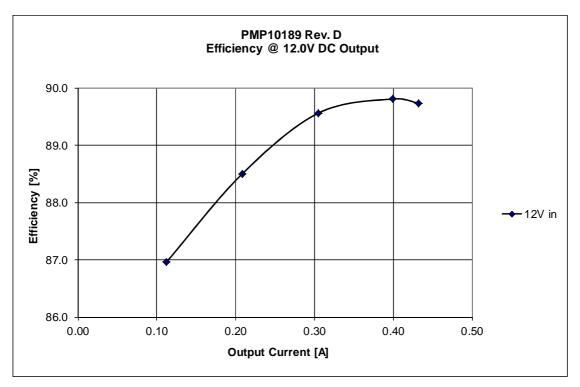

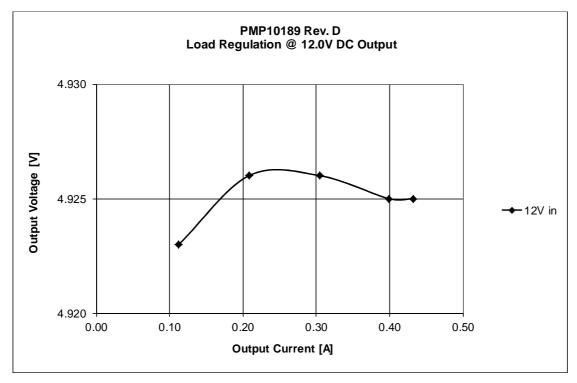

### 3.5 Efficiency & Load Regulation

The efficiency and load regulation are shown in Figure 17 and Figure 18.

Figure 17

Figure 18

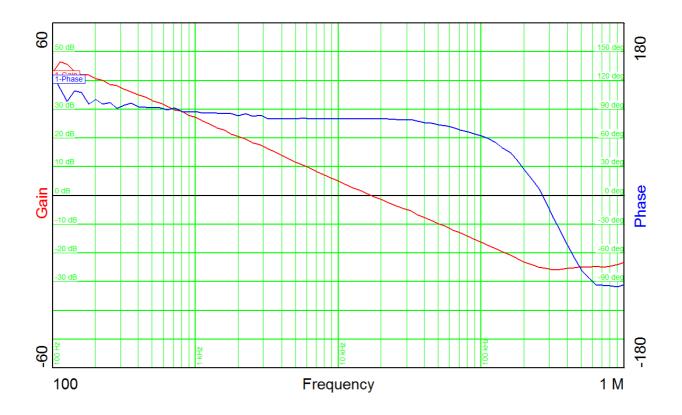

### 3.6 Frequency Response

Figure 19 shows the loop response at 12.0V input voltage and 430mA load.

#### 12V input

• 430mA load 80 deg phase margin, 17.1 kHz bandwidth, -25 dB gain margin

Figure 19

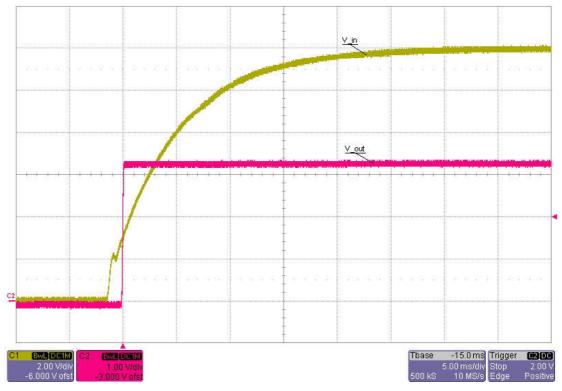

## 4 TLV62080 - +1.2V @ 700mA

### 4.1 Startup

The startup waveform is shown in Figure 20. The input voltage is set at 5.0V with no load on the 1.2V output.

Channel C1: **5.0V Input voltage**

2V/div, 5ms/div

Channel C2: **1.2V Output voltage**

Figure 20

### 4.2 Shutdown

The shutdown is shown in Figure 21. The input voltage is set at 5.0V with 700mA load on the output.

Channel C1: **5.0V Input voltage**

1V/div, 2ms/div

Channel C2: **1.2V Output voltage**

500mV/div, 2ms/div

Figure 21

### 4.3 Switching Node

The drain-source voltage on the switching node is shown in Figure 22. The image is captured with 5V input voltage and 700mA load on the 1.2V output.

Channel C2: **Drain-source voltage**, -1.0V minimum voltage, 5.0V maximum voltage 1V/div, 500ns/div

Figure 22

### 4.4 Output Ripple

The output ripple voltage is shown in Figure 23. The input voltage is set at 5.0V with 700mA load on the output.

Channel C2: **Output voltage** @ **5.0V input**, 2mV peak-peak (0.2%) 20mV/div, 1us/div, AC coupled

Figure 23

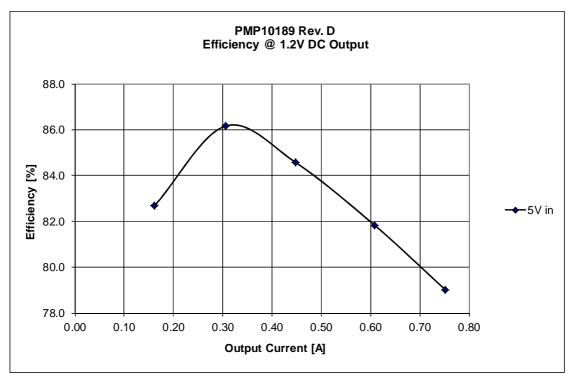

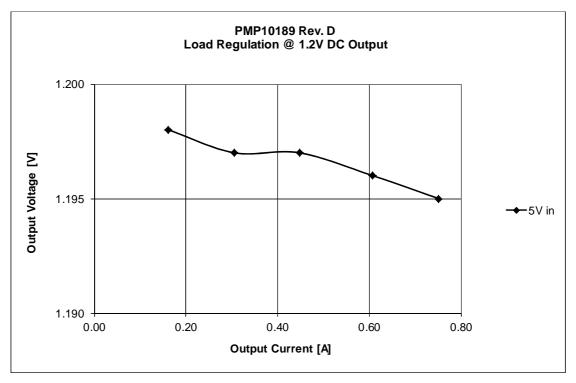

### 4.5 Efficiency & Load Regulation

The efficiency and load regulation are shown in Figure 24 and Figure 25.

Figure 24

Figure 25

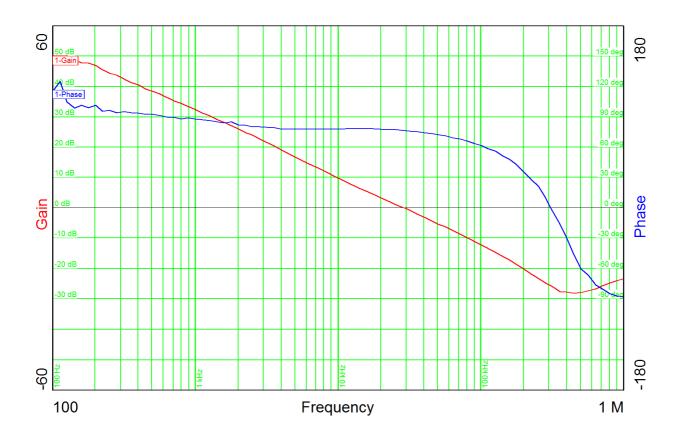

### 4.6 Frequency Response

Figure 26 shows the loop response at 5.0V input voltage and 700mA load.

#### 5V input

• 700mA load 77 deg phase margin, 28.5 kHz bandwidth, -26 dB gain margin

Figure 26

## 5 TPS62160 - +3.3V @ 620mA

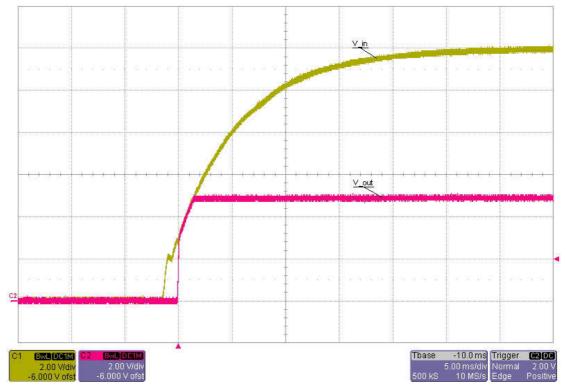

### 5.1 Startup

The startup waveform is shown in Figure 27. The input voltage is set at 12.0V with no load on the 3.3V output.

Channel C1: **12.0V Input voltage**

2V/div, 5ms/div

Channel C2: 3.3V Output voltage

Figure 27

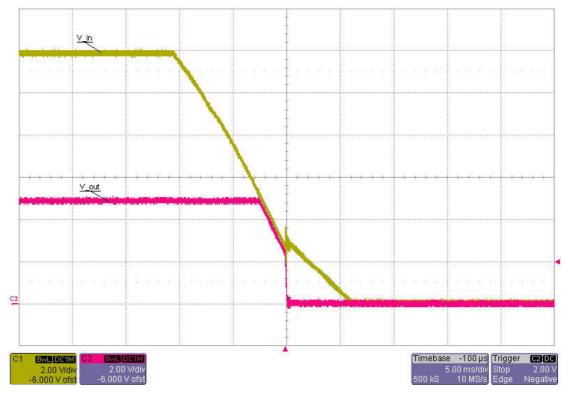

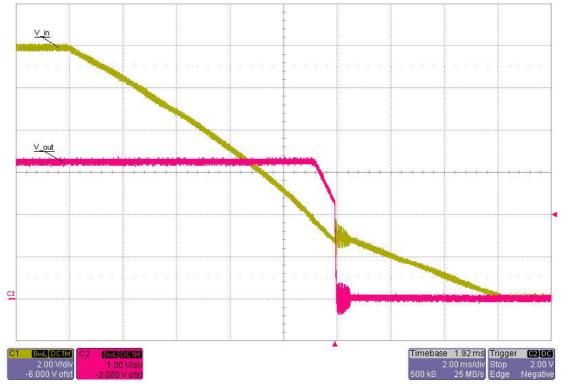

#### 5.2 Shutdown

The shutdown is shown in Figure 28. The input voltage is set at 12.0V with 620mA load on the output.

Channel C1: 12.0V Input voltage

2V/div, 2ms/div

Channel C2: **3.3V Output voltage**

Figure 28

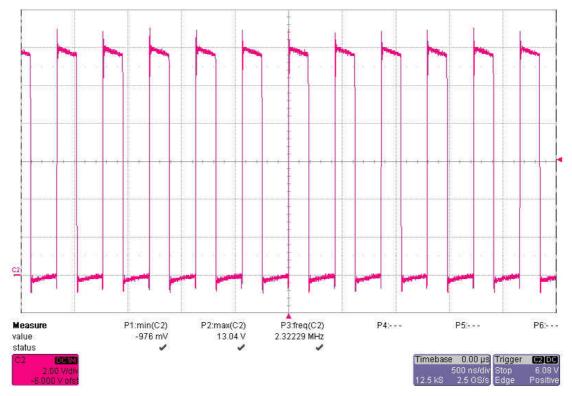

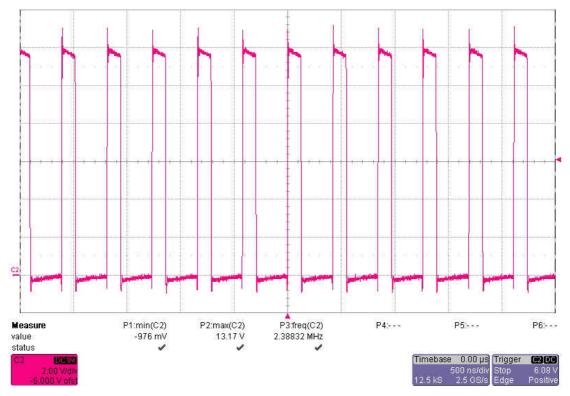

### 5.3 Switching Node

The drain-source voltage on the switching node is shown in Figure 29. The image is captured with 12V input voltage and 620mA load on the 3.3V output.

Channel C2: **Drain-source voltage**, -1.0V minimum voltage, 13.2V maximum voltage 2V/div, 500ns/div

Figure 29

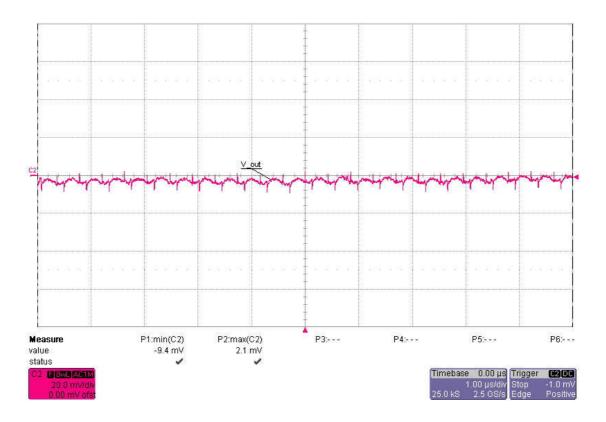

### 5.4 Output Ripple

The output ripple voltage is shown in Figure 30. The input voltage is set at 12.0V with 620mA load on the output.

Channel C2: **Output voltage** @ **12.0V input**, 10mV peak-peak (0.3%) 20mV/div, 1us/div, AC coupled

Figure 30

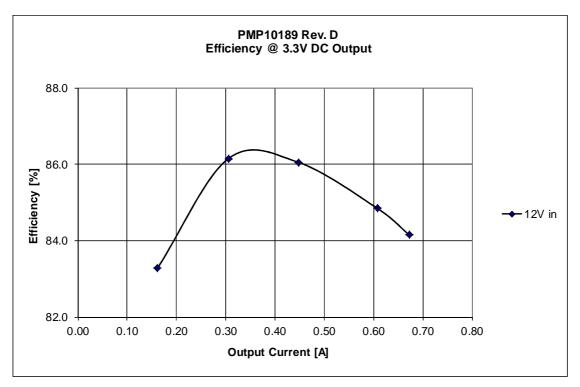

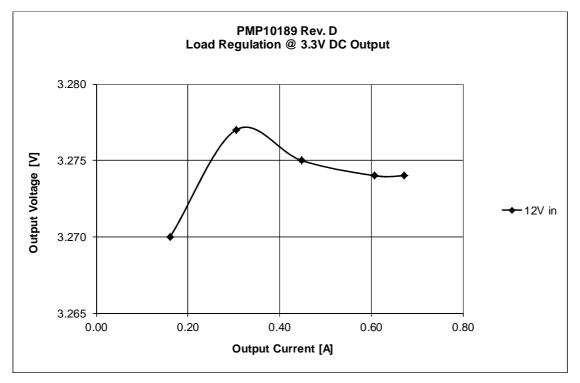

### 5.5 Efficiency & Load Regulation

The efficiency and load regulation are shown in Figure 31 and Figure 32.

Figure 31

Figure 32

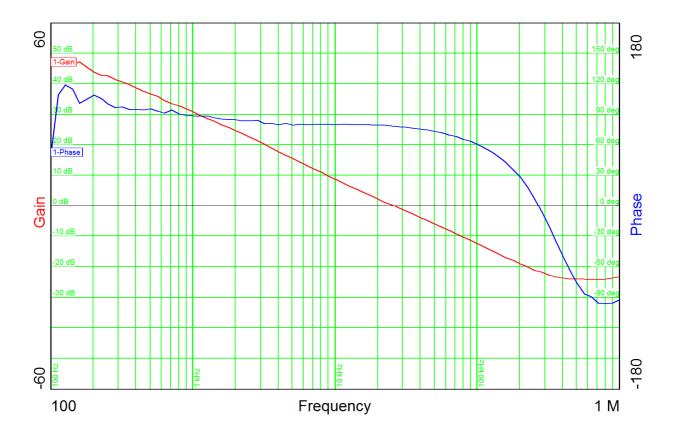

### **5.6** Frequency Response

Figure 33 shows the loop response at 12.0V input voltage and 620mA load.

#### 12V input

• 620mA load 78 deg phase margin, 25.8 kHz bandwidth, -22 dB gain margin

Figure 33

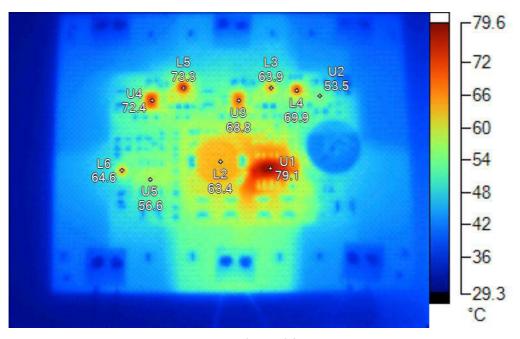

## **6** Thermal Measurement

The thermal image (Figure 34) shows the circuit at an ambient temperature of  $21~^{\circ}$ C with an input voltage of 54.0V and full load on all outputs.

Figure 34

#### Markers

| Name | Temperature | Emissivity | Background |

|------|-------------|------------|------------|

| L6   | 64.6°C      | 0.95       | 21.0°C     |

| U5   | 56.6°C      | 0.95       | 21.0°C     |

| L2   | 63.4°C      | 0.95       | 21.0°C     |

| U1   | 79.1°C      | 0.95       | 21.0°C     |

| U4   | 72.4°C      | 0.95       | 21.0°C     |

| L5   | 73.3°C      | 0.95       | 21.0°C     |

| U3   | 68.8°C      | 0.95       | 21.0°C     |

| L3   | 63.9°C      | 0.95       | 21.0°C     |

| L4   | 69.9°C      | 0.95       | 21.0°C     |

| U2   | 53.5°C      | 0.95       | 21.0°C     |

#### IMPORTANT NOTICE FOR TI REFERENCE DESIGNS

Texas Instruments Incorporated ("TI") reference designs are solely intended to assist designers ("Buyers") who are developing systems that incorporate TI semiconductor products (also referred to herein as "components"). Buyer understands and agrees that Buyer remains responsible for using its independent analysis, evaluation and judgment in designing Buyer's systems and products.

TI reference designs have been created using standard laboratory conditions and engineering practices. TI has not conducted any testing other than that specifically described in the published documentation for a particular reference design. TI may make corrections, enhancements, improvements and other changes to its reference designs.

Buyers are authorized to use TI reference designs with the TI component(s) identified in each particular reference design and to modify the reference design in the development of their end products. HOWEVER, NO OTHER LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE TO ANY OTHER TI INTELLECTUAL PROPERTY RIGHT, AND NO LICENSE TO ANY THIRD PARTY TECHNOLOGY OR INTELLECTUAL PROPERTY RIGHT, IS GRANTED HEREIN, including but not limited to any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services, or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

TI REFERENCE DESIGNS ARE PROVIDED "AS IS". TI MAKES NO WARRANTIES OR REPRESENTATIONS WITH REGARD TO THE REFERENCE DESIGNS OR USE OF THE REFERENCE DESIGNS, EXPRESS, IMPLIED OR STATUTORY, INCLUDING ACCURACY OR COMPLETENESS. TI DISCLAIMS ANY WARRANTY OF TITLE AND ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, QUIET ENJOYMENT, QUIET POSSESSION, AND NON-INFRINGEMENT OF ANY THIRD PARTY INTELLECTUAL PROPERTY RIGHTS WITH REGARD TO TI REFERENCE DESIGNS OR USE THEREOF. TI SHALL NOT BE LIABLE FOR AND SHALL NOT DEFEND OR INDEMNIFY BUYERS AGAINST ANY THIRD PARTY INFRINGEMENT CLAIM THAT RELATES TO OR IS BASED ON A COMBINATION OF COMPONENTS PROVIDED IN A TI REFERENCE DESIGN. IN NO EVENT SHALL TI BE LIABLE FOR ANY ACTUAL, SPECIAL, INCIDENTAL, CONSEQUENTIAL OR INDIRECT DAMAGES, HOWEVER CAUSED, ON ANY THEORY OF LIABILITY AND WHETHER OR NOT TI HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES, ARISING IN ANY WAY OUT OF TI REFERENCE DESIGNS OR BUYER'S USE OF TI REFERENCE DESIGNS.

TI reserves the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques for TI components are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

Reproduction of significant portions of TI information in TI data books, data sheets or reference designs is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards that anticipate dangerous failures, monitor failures and their consequences, lessen the likelihood of dangerous failures and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in Buyer's safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed an agreement specifically governing such use.

Only those TI components that TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components that have *not* been so designated is solely at Buyer's risk, and Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of non-designated products, TI will not be responsible for any failure to meet ISO/TS16949.