# TI Designs

# PCI-Express PCB Design Considerations Reference Design for the K2G2x General Purpose EVM (GP EVM)

# 1 Trademarks

KeyStone, BeagleBone are trademarks of Texas Instruments. ARM is a registered trademark of ARM Limited. All other trademarks are the property of their respective owners.

# **TI Designs**

TI Designs provide the foundation that you need including methodology, testing and design files to quickly evaluate and customize the system. TI Designs help *you* accelerate your time to market.

# **Design Resources**

TIDEP0068

TI Design Folder

High Speed Layout

Guidelines

66AK2G02

Product Folder

Product Folder

Product Folder

Product Folder

Tool Folder

Processor SDK for K2G

TI Design Folder

Product Folder

Tool Folder

Software Folder

ASK Our E2E Experts

#

# **Design Features**

- · Optimized High-Speed Signal Routing

- Surface-Mount PCIe x 1 Socket

- Example of AC Coupling Capacitor Placement

- Example of Recommended Differential Pair Spacing

# **Featured Applications**

- Power Protection

- Industrial Communications and Control

- Substation Automation

- · Grid Communications

A

An IMPORTANT NOTICE at the end of this TI reference design addresses authorized use, intellectual property matters and other important disclaimers and information.

# 2 66AK2G02 and Featured Applications

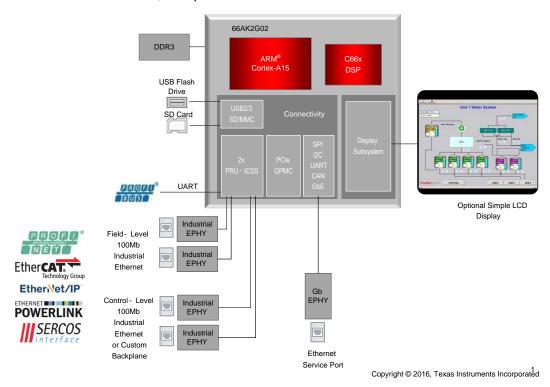

The 66AK2G02 supports the following features (refer to the 66AK2G02 block diagram on page 1):

- Processor Cores and Memory

- ARM Cortex A15 at 600 MHz

- C66x DSP at 600 MHZ

- 32 KB L1D, 32 KB L1P, 512 KB L2 cache

- · Ecc on all memory

# Industrial and Control Peripherals

- 2 Industrial Communication Subsystems enable cut through, real-time and low latency Industrial Ethernet protocols

- Programmable real-time I/O enables versatile field bus and control interfaces

- PCIe for connection to an FPGA or ASIC that provides industrial network connections, backplane communication, or connection to another 66AK2G02 device.

- Security and Crypto

- Standard secure boot with customer programmable OTP keys

- Crypto

- Package

- 21 x 21 mm^2, 0.8 mm pitch BGA 625 pins

The 66AK2G02 is suited for applications such as Industrial PLC and Protection Relay as shown in Figure 1 and Figure 2. In these systems PCIe is used for connection to an FPGA or ASIC that provides industrial network connections, backplane communication or connection to another 66AK2G02 device.

Figure 1. Industrial PLC System Block Diagram

Copyright © 2016, Texas Instruments Incorporated

Figure 2. Protection Relay System Block Diagram

Design Overview www.ti.com

# 3 Design Overview

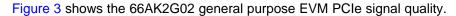

The 66AK2G02 SoC is a high-performance, highly integrated device based on TI KeyStone™ II Multicore DSP + ARM® System-on-Chip (SoC) architecture. The device incorporates a single-lane PCI-Express (PCIe) Gen2 (5GT/s) module that may perform as either a Root Complex (RC) or End Point (EP) device. This design discusses the implementation of the PCI-Express interface on the 66AK2G02 General Purpose EVM with an eye toward optimizing signal integrity of the interface.

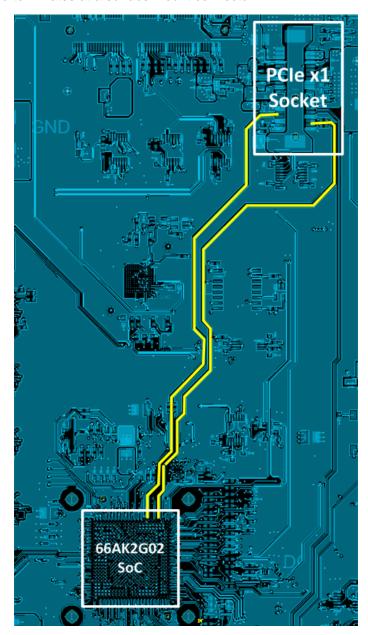

Figure 3. 66AK2G02 General Purpose EVM PCIe Signal Quality

# 4 Key System Specifications

The PCI-Express module present in the 66AK2G02 device supports both Root-Complex and End Point operation on a single-lane bidirectional link interface. PCIe provides for low pin-count, high reliability, and high-speed with data transfer at rates of up to 5.0 Gbps per lane, per direction. PCIe is intended for use as a serial link on backplanes and printed circuit boards. The 66AK2G02 GP EVM provides a PCIe ×1 add-in card socket to ease evaluation of PCIe EP's prior to implementation in a custom design. The GP EVM does not provide an interface for testing the device as an EP.

System Description www.ti.com

### 5 **System Description**

The intent of this TI Design is to provide PCB layout considerations for the PCle portion of the 66AK2G02 System-on-Chip (SoC). The 66AK2G02 GP EVM is used as a reference to discuss some of these considerations. A more detailed explanation of concepts discussed in this document as well as further information and recommendations on high-speed layout considerations may be found in the High-Speed Interface Layout Guidelines (SPRAAR7E).

NOTE: As with all PCB designs, best performance with regard to signal integrity is contingent on performing a board-level simulation and reviewing the results prior to committing the design to PCB. Every PCB design must be evaluated independently as no two are alike.

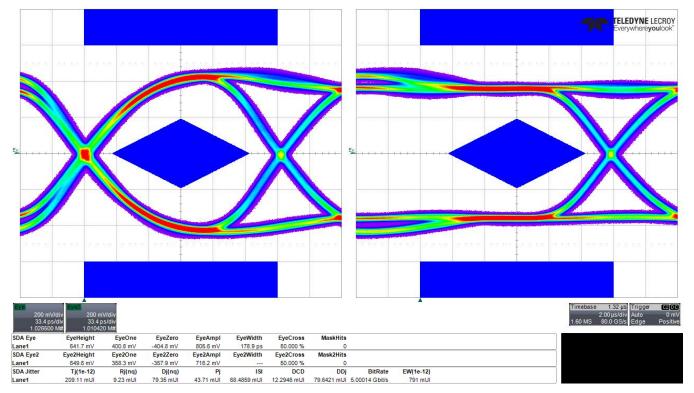

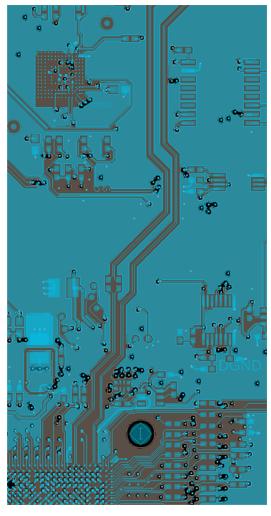

### 66AK2G02 GP EVM - All Layers 5.1

Figure 4 shows the entirety of the GP EVM design.

Figure 4. 66AK2G02 GP EVM - All Layers

System Description www.ti.com

# 5.2 66AK2G02 GP EVM - Top Layer - Routing

When designing a PCB that incorporates one or more high-speed interfaces, it is critical that the high-speed signals are routed early in the board design process, preferably first. Routing early ensures that all signals are routed without obstructions or abutments that may force an inclusion of a via, or crossing (unnecessary extension) of the high-speed signals. Care must be given to the physical relationship of the devices that comprise the PCIe bus. Figure 5 shows that the PCIe x1 socket is placed in such a way that the PCIe signals from the SoC PCIe Root Complex to the socket flow naturally; no rotating of the SoC or socket is required. Place the socket in a position that allows it to accept the signals without the need for vias to improve signal quality. For the 66AK2G02 GP EVM, the PCIe interface has been routed completely on the top layer and terminates at a surface mount connector.

Figure 5. 66AK2G02 GP EVM - Top Layer Only - Zoomed

www.ti.com System Description

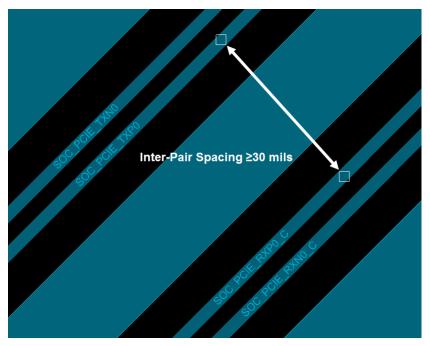

# 5.3 66AK2G02 GP EVM – Top Layer – Differential Signal Spacing

To minimize crosstalk in high-speed interface implementations, the spacing between the signal pairs must be a minimum of 5 times the width of the trace. This spacing is referred to as the *5W rule*. A PCB design with a calculated trace width of 6 mils requires a minimum of 30 mils spacing between high-speed differential pairs. Also, maintain a minimum keep-out area of 30 mils to any other signal throughout the length of the trace. Where the high-speed differential pairs abut a clock or a periodic signal, increase this keep-out to a minimum of 50 mils to ensure proper isolation. When possible, the keep-out area should be maximized to further reduce the possibility of crosstalk. In the case of the 66AK2G02 GP EVM, the PCB was of sufficient size to allow spacing that exceeds 65 mils in many locations. Figure 6 shows the 66AK2G02 GP EVM inter-pair spacing.

Figure 6. 66AK2G02 GP EVM Inter-Pair Spacing

System Description www.ti.com

# 5.4 66AK2G02 GP EVM - Top Layer - Reference Plane

High-speed signals should be routed over a solid ground reference plane and should not cross or directly abut a void in the reference plane. TI does not recommend high-speed signal references to power planes. Routing across a plane split or a void in the reference plane forces return high-frequency current to flow around the split or void, which may result in the following conditions:

- 1. Excess radiated emissions from an unbalanced current flow

- 2. Delays in signal propagation delays due to increased series inductance

- 3. Interference with adjacent signals

- 4. Degraded signal integrity (that is, more jitter and reduced signal amplitude)

In keeping with the above recommendations, the 66AK2G02 GP EVM routes the PCle signals over an unbroken, ground reference plane as shown in Figure 7.

Figure 7. 66AK2G02 GP EVM PCIe Reference Plane

www.ti.com System Description

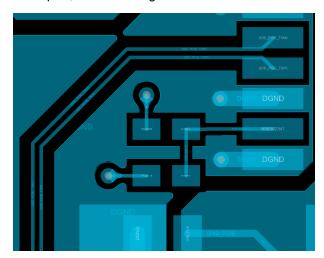

# 5.5 66AK2G02 GP EVM – Top Layer – Symmetrical Routing

Because PCIe is a differential interface, all routing of the member pairs must be symmetrical and maintain as much parallelism as possible as they traverse the board together. In the case of the 66AK2G02 GP EVM, observe in Figure 8 that the *PCIE\_TXN0* and *PCIE\_TXP0* signals maintain symmetry and parallelism across the board up to, and including the PCIe x1 add-in card socket pads.

Figure 8. Symmetrical Routing and Parallelism of PCle Signal Pair

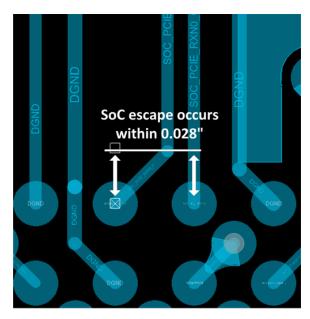

The symmetry and requirements apply to both ends of the interface, however, it may be impossible to fully meet the requirements when routing SoC escape of the PCle signals. In this particular case, it is permissible to deviate from both symmetry and parallelism for up to 0.25" when escaping the SoC. For 66AK2G02 GP EVM, SoC escape of the PCle signals is complete at ±28mils, well within the 0.25" (250 mil) limit.

Figure 9. SoC Escape

Design Files www.ti.com

# 6 Design Files

The design files for the 66AK2G02 General Purpose EVM may be found at <a href="http://www.ti.com/tool/TIDEP0068">http://www.ti.com/tool/TIDEP0068</a>.

# 7 References

1. High-Speed Interface Layout Guidelines, (SPRAAR7E)

www.ti.com About the Author

# 8 About the Author

**DAVE KING** is a Senior Hardware Applications Engineer in TI's Embedded Processing organization supporting a wide array of ARM-based SoCs such as AM335x (as found on BeagleBone™ and BeagleBone Black), AM35x, AM37x, AM57xx, and AM437x. Dave brings to this role more than fifteen years of protocol, digital, and analog experience in high-speed interfaces ranging from PCI-Express to USB2.0/3.1.

## IMPORTANT NOTICE FOR TI DESIGN INFORMATION AND RESOURCES

Texas Instruments Incorporated ("TI") technical, application or other design advice, services or information, including, but not limited to, reference designs and materials relating to evaluation modules, (collectively, "TI Resources") are intended to assist designers who are developing applications that incorporate TI products; by downloading, accessing or using any particular TI Resource in any way, you (individually or, if you are acting on behalf of a company, your company) agree to use it solely for this purpose and subject to the terms of this Notice.

TI's provision of TI Resources does not expand or otherwise alter TI's applicable published warranties or warranty disclaimers for TI products, and no additional obligations or liabilities arise from TI providing such TI Resources. TI reserves the right to make corrections, enhancements, improvements and other changes to its TI Resources.

You understand and agree that you remain responsible for using your independent analysis, evaluation and judgment in designing your applications and that you have full and exclusive responsibility to assure the safety of your applications and compliance of your applications (and of all TI products used in or for your applications) with all applicable regulations, laws and other applicable requirements. You represent that, with respect to your applications, you have all the necessary expertise to create and implement safeguards that (1) anticipate dangerous consequences of failures, (2) monitor failures and their consequences, and (3) lessen the likelihood of failures that might cause harm and take appropriate actions. You agree that prior to using or distributing any applications that include TI products, you will thoroughly test such applications and the functionality of such TI products as used in such applications. TI has not conducted any testing other than that specifically described in the published documentation for a particular TI Resource.

You are authorized to use, copy and modify any individual TI Resource only in connection with the development of applications that include the TI product(s) identified in such TI Resource. NO OTHER LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE TO ANY OTHER TI INTELLECTUAL PROPERTY RIGHT, AND NO LICENSE TO ANY TECHNOLOGY OR INTELLECTUAL PROPERTY RIGHT OF TI OR ANY THIRD PARTY IS GRANTED HEREIN, including but not limited to any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information regarding or referencing third-party products or services does not constitute a license to use such products or services, or a warranty or endorsement thereof. Use of TI Resources may require a license from a third party under the patents or other intellectual property of TI.

TI RESOURCES ARE PROVIDED "AS IS" AND WITH ALL FAULTS. TI DISCLAIMS ALL OTHER WARRANTIES OR REPRESENTATIONS, EXPRESS OR IMPLIED, REGARDING TI RESOURCES OR USE THEREOF, INCLUDING BUT NOT LIMITED TO ACCURACY OR COMPLETENESS, TITLE, ANY EPIDEMIC FAILURE WARRANTY AND ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND NON-INFRINGEMENT OF ANY THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

TI SHALL NOT BE LIABLE FOR AND SHALL NOT DEFEND OR INDEMNIFY YOU AGAINST ANY CLAIM, INCLUDING BUT NOT LIMITED TO ANY INFRINGEMENT CLAIM THAT RELATES TO OR IS BASED ON ANY COMBINATION OF PRODUCTS EVEN IF DESCRIBED IN TI RESOURCES OR OTHERWISE. IN NO EVENT SHALL TI BE LIABLE FOR ANY ACTUAL, DIRECT, SPECIAL, COLLATERAL, INDIRECT, PUNITIVE, INCIDENTAL, CONSEQUENTIAL OR EXEMPLARY DAMAGES IN CONNECTION WITH OR ARISING OUT OF TI RESOURCES OR USE THEREOF, AND REGARDLESS OF WHETHER TI HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

You agree to fully indemnify TI and its representatives against any damages, costs, losses, and/or liabilities arising out of your non-compliance with the terms and provisions of this Notice.

This Notice applies to TI Resources. Additional terms apply to the use and purchase of certain types of materials, TI products and services. These include; without limitation, TI's standard terms for semiconductor products <a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation modules, and samples (<a href="http://www.ti.com/sc/docs/sampterms.htm">http://www.ti.com/sc/docs/sampterms.htm</a>).

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2018, Texas Instruments Incorporated